基于FPGA的无线通信收发模块设计方案

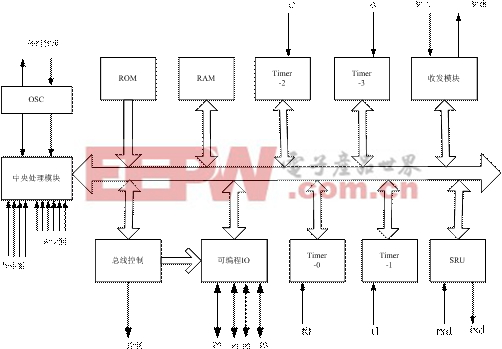

该处理系统的主要功能模块有:

核心控制模块

总线控制模块

可编程中断处理模块

可编程并行I/O接口(P0、P1、P2、P3)

可编程串行接口单元(SIU)

可编程定时计数器0~3(Timer0~Timer3)

可编程摩尔斯码异步收发模块

中断处理模块有4个外中断源(int0~int3)和6个内中断源(TF0~TF3、T1/R1、mT1/mR1),SIU是系统的通用串行接口,它有4种工作模式,工作模式1~3是通用串行异步接收发送USART(Universal Serial Asynchronous Receiver/Transmitter)工作方式。当SIU工作于工作模式1或3时,Timer1是其波特率发生器。

4 仿真与验证

设计的验证包括功能仿真、时序仿真和电路验证。仿真验证往往是借助第3方提供的EDA开发工具软件包或专用仿真工具软件来实现的。电路验证还需要开发验证平台,对于系统级芯片验证平台的设计也是一项艰巨而不能回避的任务。

本文选用的是Altera公司的MaxPlusII作EDA开发工具,MaxPlusII编译器支持功能仿真(前仿真)和时序仿真(后仿真)。完成源代码(VHDL)设计输入之后,若要进行功能仿真,则在MaxplusII/Compile下,通过选择Processing菜单下的Functional SNF Extractor命令,打开功能仿真器网表文件(SNF)提取器,再进行编译仿真;若要进行定时模拟(时序)仿真,则须在MaxPlusII/Compile下,选择Processing菜单中的Timing SNF Extractor命令,打开定时模拟器网表文件提取器来进行编译仿真。

电路验证就是器件编程测试过程。对于常规的芯片设计,时序仿真结束后,仿真软件就可以产生供器件编程使用的数据文件。对EPLD/CPLD来说,是产生熔丝图文件,即JED文件,对于FPGA来说,是产生位流数据文件(Bitstream Generation),然后将编程数据下载到对应的具体可编程器件中去,然后对其进行实际环境的电路测试。

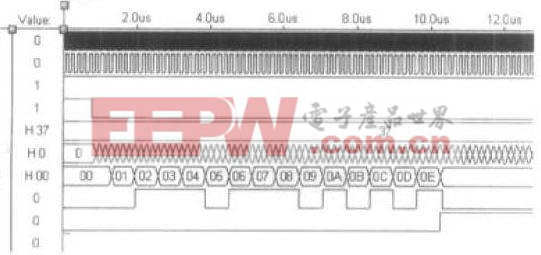

本文选择CLK频率为25MHZ,波特率为25M/16=1562500bps。当发送字符‘7’,执行发送命令后,将启动数据发送的进程,将字符‘7’的ASCLL码值送入ASCLL码发送缓存器,通过MaxPlusII的Simulator仿真器,进行时序仿真验证,研究结果如图三所示。从图中可看出,串行信号端子输出的“2长划”,“3点”,经查表对应的就是摩尔斯数字‘7’,证明数据发送是正确的。另外当数据输出结束后,立刻置高电平,即产生中断信号mTI,字符‘7’的发送用时大约10us。

图 三:仿真验证数据

5 创新点总结

本文的创新点在于提出了一种基于FPGA的无线通信收发模块,并以当今海事通信中占重要地位的摩尔斯电码为例,研究了摩尔斯电码的数字化编码方法,并通过大量的分析设计和实验仿真,实现了基于FPGA处理摩尔斯电码的收发模块,仿真结果也验证了本文所设计的摩尔斯电码数字化编码方法正确可行,工作运行可靠。

评论