基于CPCI总线和TS201的通用雷达信号处理板设计

2.3 PCI9656与CPCI总线连接设计

设计中信号处理板是6U规格,可与J1至J5五个连接头相连。J1是32位PCI总线,J2用于64位PCI总线或用户自定义I/O口;J3,J4和J5是用户自定义I/O口。为了保证信号处理板的通用性和可扩展性,J1与J2连接头作为64位数据宽度的CPCI总线。PCI9656一端与FPGAl相连另一端分别与儿和J2连接头相连。需要注意的是PCI9656与CPCI连接的引脚必须插入10 Ω的匹配电阻,以降低对背板的干扰。

2.4 Rocket_IO与DSP的连接设计

信号处理板通过全双工Rocket_IO口接收板外的采集数据,数据吞吐率可达1.25 Gb/s。FPGA2实现Rocket_IO与DSP的LinkPort之间的接口转换,其一端连接4路Rocket_IO口相连另一端连接每片DSP的1路LinkPort,即4路链路口。

DSP的每路链路口数据吞吐率可达,1 GB/s。FPGA2对.Rocket_IO口送入的数据整理后,利用链路口传输给相应的DSP。任意一路LinkPort能与任意一路的Rocket_IO口通信,当多路LinkPort争用一路Rocket_IO口或多路Rocket_IO口争用一路LinkPort时,FPGA2内的总线开关模块实现它们之间的仲裁。设计中信号处理板可以选用任意用户自定义IO口作为Rocket_IO通道。本文引用地址:http://www.eepw.com.cn/article/158083.htm

3 PCI9656与DSP的接口设计

PCI9656的局部端采用C模式,32位数据和32位地址线。PCI9656配置为直接从模式,即只有主机可以通过PCI9656申请局部端总线控制权访问DSP。4片DSP与FPGAl连接方式相同,这里只给出1片DSP与PCI9656之间的接1:3逻辑转换。DSP和PCI9656的连接如图2所示。

PCI9656对DSP的访问通过FPGAl间接实现,FPGAl内设计有实现逻辑转换的主机接口模块、用于数据缓存的双口RAM模块和DSP开关选择模块。

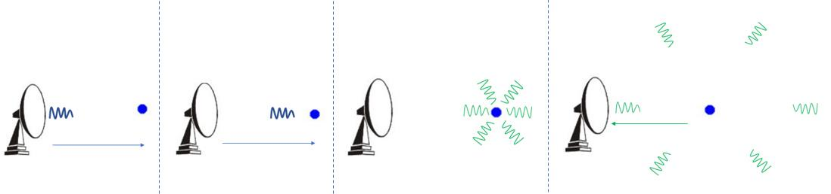

3.1 PCI9656读DSP

(1)PCI9656使LHOLD变高申请局部总线控制权;FPGA检测到后,立即使LHOLDA变高,告知PCI9656局部总线申请成功。PCI9656使ADS和一LW/R变低,然后发送主机地址;FPGAl依据高位地址译码生成DSP片选信号,根据LW/R将主机接口配置为读方式,同时使PCI9656的READY信号无效。

(2)FPGAl向相应的DSP发HBR和RD申请总线控制权并请求读数据;DSP检测到HBR后返回HBG和ACK。FPGAl检测ACK到信号后,接收数据并缓存至双口RAM。当数据传输完毕时DSP使RD和ACK无效,撤销HBG,FPGAl接着撤销HBR。

(3)FPGAl使READY有效,PCI9656检测到该信号后,开始读取双口RAM中的数据。数据传输完毕后FPGAl使READY无效并收回LHOLDA,PCI9656接着撤消LHOLD,此次读操作结束。

3.2 PCI9656写DSP

(1)PCI9656使LHOLD变高申请局部总线控制权;FPGA检测到后,立即回应使LHOLDA变高告知PCI9656局部总线申请成功。PCI9656使ADS变低、LW/R变高,然后发送主机地址;FPGAl根据高位地址译码生成DSP片选信号,根据LW/R将主机接口配置为写方式,同时使能PCI9656的READY。

(2)PCI9656检测到READY后,将数据写入双口RAM。数据传输完毕后PCI9656使READY无效,收回LHOLD;FPGAl接着撤消LHOLDA。

(3)FPGAl向相应的DSP发出HBR和WRL申请总线控制权并请求对DSP写数据操作,DSP检测到信号返回HBG和ACK。FPGAl检测到ACK信号后,开始将双口RAM中的数据发送给DSP。数据传输完毕后FPGA使WRL无效,撤销HBR;DSP接着撤销HBG和ACK。此次写操作完成。

4 结 语

提出的基于CPCI总线的高速通用雷达信号处理板设计,继承了CPCI总线可靠、可扩展、通用性强的特点。PCI9656桥芯片和FPGAl逻辑转换芯片实现板外主机对DSP的访问。通过FPGA2将Rocket_IO口与DSP的LinkPort口互联实现数据的高速传输。

评论