一种基于ADSP-BF537的无线视频传输方案

对DSP而言,DSP通过外部总线连接到SRAM0和SRAM1,这就相当于外扩了两个外部RAM,DSP可以自由地访问它们。图2中的SRAM0,SRAM1分别用于DSP发送数据和接收数据。SRAM0和SRAM1本身是双口RAM,可以供DSP和FPGA访问,就是通过这种共享存储器的方式完成数据交互。

2.3 软件系统结构

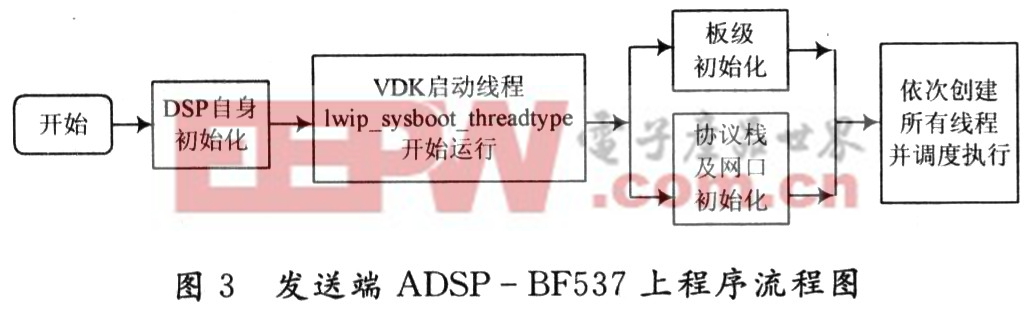

相关程序是用含有VDK(Visual DSP Kernel)的DSP软件开发工具Visual DSP开发的。VDK是一种带有API函数库的实时操作系统内核,它具有任务调度和任务管理功能,一共支持32个任务。VDK是整个软件的基础,所有其他的程序都运行在该Kernel上。程序流程图如图3所示。

上电或复位后,DSP自启动后VDK启动线程lwip_sysboot_threadtype开始运行。在线程lwip_sysboot_threadtype中进行板级初始化和Lwip协议栈和网口初始化,其中板级初始化包括FPGA初始化,EBIU初始化,MDMA初始化,FLAG初始化。接下来创建下面几个线程:

(1)数据传输:视频数据传输。用于从编码器获取编码后的视频数据流,并存储到缓冲区中。

(2)FPGA中断:视频数据发送中断;MDMA中断。

DSP首先通过Socket与视频服务器连接,从视频服务器获取视频数据,并将数据缓存后按照特定的格式打包,等待FPGA触发视频数据发送中断。中断触发后,DSP启动MDMA将一帧大小的数据发送给FPGA发送缓冲区。当MDMA操作完成后,触发MDMA中断,将帧头写入FPGA发送缓冲区的头两个字节。FPGA将接收的数据进行基带算法处理后再将数据发送给射频部分,之后FPGA再触发视频数据发送中断,告诉DSP可以下一帧的发送,于是又启动MDMA,如此循环。

3 实验结果和分析

对系统在不同的信噪比的环境中传输的误码率进行了测试。测试方法如下:将发射机的输出端口通过数据排线与逻辑分析仪相连,逻辑分析仪将采集到的一帧发射信号送到PC中用Matlab软件对其加上噪声,得到信噪比固定的信号。将这个信号导人信号源中进行不间断循环发送给接收端的输入端口。接收机接收信号进行解调并将解调出的数据传给PC以统计误码率。测试结果如表2所示。

4 结 语

设计了一种无线视频传输系统的方案,并对其中发射部分的数据通信过程做了详细阐述。从硬件架构和软件设计两方面说明了数据在视频服务器、DSP和FP-GA之间的传递过程。其中ADSP-BF537作控制器,成功完成了动态配置FPGA和通过网口传送视频数据的功能。该方案很好地满足了大数据量,实时性的数据处理和结构灵活,模块化设计相结合的要求。同时DSP+FPGA的数字硬件系统开发周期较短,系统容易维护和扩展,适合实时信号处理,使方案有更广泛的应用。

评论