10~37 GHz CMOS四分频器的设计

该四分频器采用UMC 0.13μm 1层多晶硅和8层金属的CMOS混合信号工艺技术。首先利用UMC公司提供的库文件在HSPICE软件下对电路进行前仿真,然后在Cadence环境下进行版图设计并提取寄生参数后,对电路后仿真。图3为四分频器的版图。其芯片面积为(0.33x0.28)mm2。

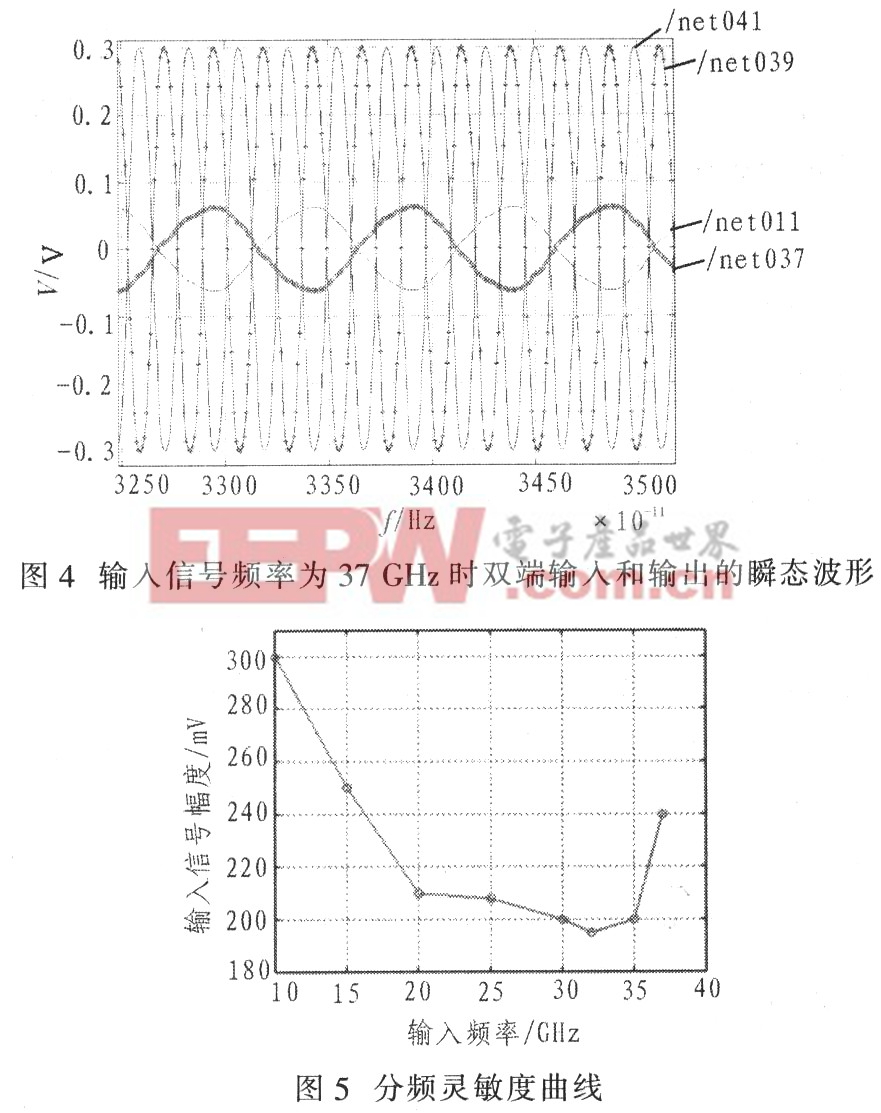

分频器在最高工作频率37 GHz下的差分双端输入和输出的后仿真波形如图4所示。图5为该分频器的分频灵敏度曲线。从图5可看出,该分频器工作在32 GHz附近时,所需单端输入信号幅度为180 mV。分频器在10~37 GHz的频率范围内都可以正常工作。本文引用地址:http://www.eepw.com.cn/article/157735.htm

4 结论

介绍一种超高速,宽分频范围的四分频器的设计。后仿真结果表明该四分频器的最高工作频率为37 GHz,当输入信号的幅度为300 mV时,分频范围为27 GHz。在电源电压为1.2 V,工作在37 GHz时,该电路的功耗小于30 mW。该四分频器可应用于光纤通信和其他超高速电路。

评论