高速数字电路的信号完整性与电磁兼容性设计

3 高速数字电路设计仿真举例

在一个已有的PCB板上分析和发现信号完整性问题是一件非常困难的事情,即使找到了问题,在一个已成形的板上实施有效的解决办法也会花费大量时间和费用。所以我们期望能够在物理设计完成之前查找、发现,并在电路设计过程中消除或改善信号完整性问题,这就是EDA工具需要完成的任务。先进的EDA信粤完整性工具可以仿真实际物理设计中的各种参数,对电路中的信号完整性问题进行深入细致的分析。

新一代的EDA信号完整性工具主要包括布线前/后SI分析工具和系统级SI分析工具等。使用布线前SI分析工具可以根据设计对信号完整性与时序的要求,在布线前帮助设计者选择元器件、调整元器件布局、规划系统时钟网络和确定关键线网的端接策略。SI分析与仿真工具不仅可以对一块PCB板的信号流进行分析,而且可以对同一系统内其他组成部分(如背板、连接器、电缆及其接口)进行分析,这就是系统级的SI分析工具。

针对系统级评价的SI分析工具可以对多板、连接器、电缆等系统组成元件进行分析,并可通过设计建议来帮助设计者消除潜在的SI问题,它们一般都包括IBIS模型接口、2维传输线与串扰仿真、电路仿真、SI分析结果的图形显示等功能。这类工具可以在设计包含的多种领域,如电气、EMC、热性能及机械性能等方面,综合考虑这些因素对SI的影响及这些因素之间的相互影响,从而进行真正的系统级分析与验证。例如Mentor Graphics公司的HyperLynix、ICX设计工具可以在时序与电气规则的驱动下进行板级仿真和信号线的线级仿真,并提供多板分析功能,是典型的系统级SI工具。

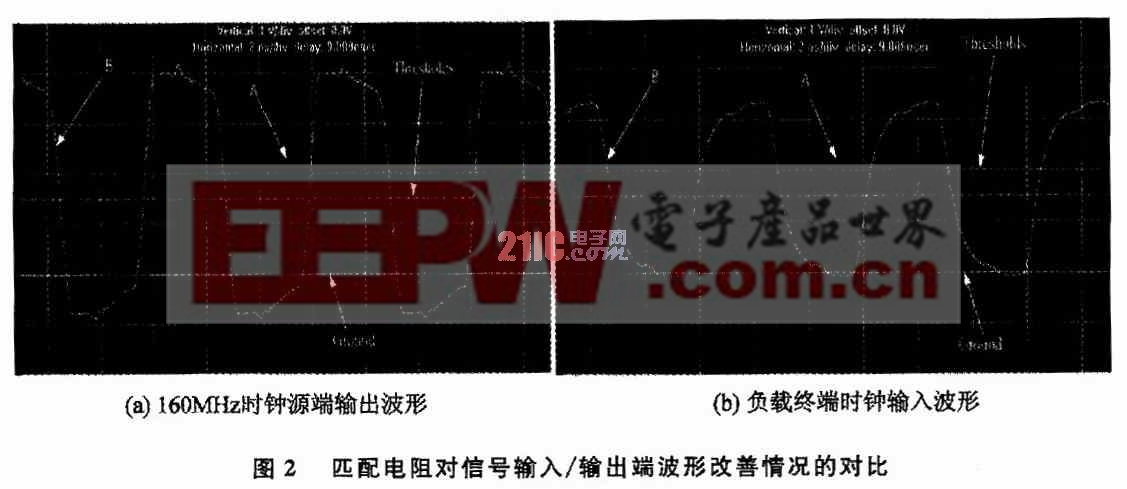

图2是使用HyperLynix进行PCB信号完整性分析时设计修改前后的对比图,以及相应EMC/EMI的改善情况。

图2(a)是没有加入匹配电阻的情况,可以明显看到输出端A的波形有一个大的下冲(大约1 V左右),而且波形最大幅度已经达到4 V(I/O信号是3.3 V),有很明显的反射迭加现象。输入端B的波形相当不好,由于反射造成的波形下冲和过冲点的信号幅值已经接近门槛电平,这样的时钟信号很容易造成触发器的错误操作。图2(b)是在靠近源输出端加入了一个47 Ω的匹配电阻后的波形,可以看到A和B的波形都有了明显的改善。

结语

现在IC制造工艺在以摩尔速度飞速发展,对高速PCB设计提出了更高的要求。先进的EDA仿真工具提供的各种仿真结果都非常接近真实情况,给高速数字电路设计起到了指导性的作用,使得设计的周期和反复性得到大大的减小,同时也使得电路的具体调试得到了理论性的指导。

DIY机械键盘相关社区:机械键盘DIY

评论