基于ADSP TS201的雷达信号处理机设计

2.2 系统软件设计及优化

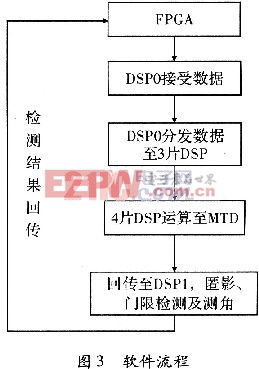

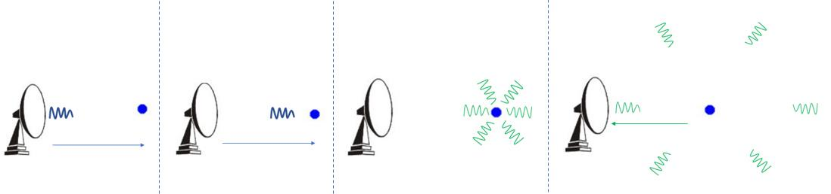

系统算法的复杂性与计算中的动态范围的要求,系统算法在DSP中软件化设计,调试方便。回波经微波合成后形成和、差路及两路辅助通道信号,A/D采样正交差值后形成4路数据经光纤传入FPGA,DSP0经总线以DMA方式接收4路数据,并分发至其它3片DSP。各DSP单独处理一路数据,如图2所示,MTD后回传至DSP1进行副瓣匿影及门限检测,并估算目标方位偏差量,检测结果由DSP1经总线以DMA方式返还至FPGA,所有的模块限制在1个脉冲周期内完成,形成了图3的软件流程图。本文引用地址:http://www.eepw.com.cn/article/157122.htm

(1)数字脉冲压缩。

系统中采用频域方法实现脉冲压缩。其基本原理是先对回波信号做FFT得其频谱S(ω),将S(ω)与匹配滤波器频谱H(ω)频域点乘,最后对乘积结果做IFFT即得脉压结果Y(n),整个过程由两次FFT,一组频域点乘,及一次IFFT运算组成,由下式表示

Y(n)=IFFT{FFT[s(n)]*FFT[h(n)]} (1)

1)针对TS201芯片内存量大的特点,将H(ω)直接存入DSP内存,以H(ω)所需内存换取了一次FFT执行时间。2)脉冲压缩结果是否乘以N对后续处理无实质影响。故IFFT的实现省略了除以N的操作,在此基础上DSP中可由两种方法实现:一种是通过改变旋转因子中正弦项的符号,调用FFT函数实现,运算速度与FFT完全一致,但保存新的旋转因子多耗费了一倍内存;另外一种则为实虚交换后做FFT,再实虚交换即实现IFF-T,该方法优点是不占用新的内存。这里在DSP程序中对第二种方法稍加改进可使处理时间与FFT完全一致:在频域点乘中结果输出时完成第一次实虚反序不占用额外指令,稍后中可看出在MTD模块中稍加改动可使脉压输出的实虚顺序并不引起系统指令的增加。原脉冲压缩处理时间为:经改进后处理时间可缩短为。内核时钟工作在600 MHz时,1 024,4 096,8 192点的频域脉压时间42.24μs、272.63μs、632.1μs,远小于脉冲重复后期,保证了系统功能的实现。

(2)MTD模块实现。

相参积累技术进一步提高了系统信噪比,使雷达在各种杂波背景下的目标检测能力提高。MTD模块用16点FFT实现,由于设计中脉冲压缩输出为先虚后实,故需对时域抽取的16点FFT第一级蝶形运算稍作修改,使对保存+j寄存器的操作与对保存re寄存器的操作互换,执行时间可与原16点FFT完全一致。

评论