超高速雷达数字信号处理技术

五、超高速数据采集系统的实现

对于1m距离分辨率的雷达系统,其采样速率可以达到250MS/s,其主要问题是:

1.体系结构的选择

(1)AD变换的体系结构[17] 在AD转换模块中,可以采用单片AD的结构,也可以采用多片AD并行的结构;而多片AD并行又包括时间并行和幅度并行两种方式.多片AD并行可以降低对每一AD芯片的性能要求,但增加了设备量和控制的复杂性.在超高速应用的场合,一般采用的是单片AD变换的结构.

(2)数据存储的体系结构[18] 由于超高速数据采集系统的速度很快,因此存储模块的设计一般都采用分路数据输出的体系结构;这种结构将AD的输出数据分成多路较低速数据输出,可以降低对存储器读写速度的要求.

2.元器件的选型与信号连线的处理

根据表1,对于250MS/s的数据采集系统,传统的TTL芯片已无法工作.目前常用的超高速标准芯片系列是ECL芯片;对于250MS/s的采样速率,ECL10KH系列可以满足要求.

根据前面的分析,超高速系统的信号连线必须采用微波传输线作为信号之间的连线,并要进行正确的端接.这样就可以消除反射,并精确控制信号的延迟.

3.模拟电路的抗干扰

系统抗干扰的方法首先是屏蔽,包括电路整体的屏蔽以及系统模拟部分和数字部分之间的屏蔽.但是由于超高速系统一般是高功耗的,因此还必须兼顾散热问题.

数据采集系统中数字电路对模拟电路的干扰是主要误差源之一.消除这一干扰可以通过器件的隔离、电源滤波、星形接地以及元器件的合理布置来解决.在超高速系统的实现中,大面积地是一个最基本、也最重要的因素之一,一方面它可以减小干扰,另一方面它也是微带传输线的一个组成部分.

4.系统的实现与性能测试

(1)系统的实现 系统中采用了单片超高速AD芯片加全局存储器的体系结构,并采用单片机构成系统与IBM-PC计算机的接口,使数据采集的结果可以在计算机中显示并加以处理(图1).其中,为降低对存储器速度的要求,采用了分路数据输出的方式,使存储器的速度降低为AD变换速度的一半.存储器的周边器件采用ECL芯片.信号之间的连线采用微带或带状传输线,并端接了合适的端接电阻.

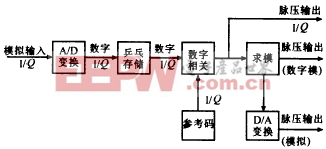

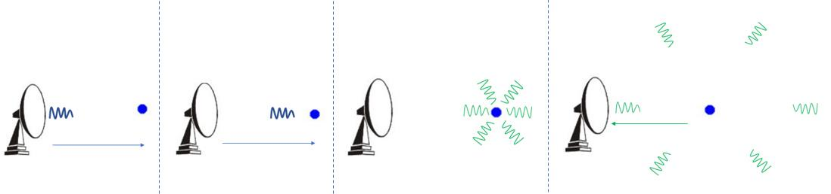

图1 超高速数据采集系统的体系结构 (2)系统性能测试 数据采集系统的性能测试主要包括静态测试和动态测试,其中动态测试更能够全面地反应系统的性能.在动态测试中最为关心的指标是动态有效位(ENOB).本系统在250MS/s采样速率、125MHz输入信号时测试了系统的动态有效位,可以证明,系统的动态有效位在7-bit以上. 六、高速数字脉冲压缩系统的实现 Y(ω)=H(ω).S(ω) (1) 这里,只要匹配滤波器的冲击响应/传递函数与发射信号满足匹配滤波关系,就可以获得脉冲压缩的输出结果. |

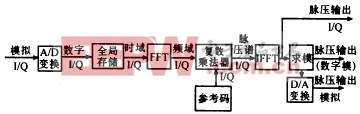

图2 时域法实现数字脉压 (2)频域法实现数字脉压 频域法实现数字脉压的基础是式(1),其基本结构示于图3.这里,采集的原始信号首先通过FFT变换到频域,与预先存储的参考码相乘后,再通过逆FFT变换回时域,就构成脉压后的数字结果;同样可以采用DA变换将其变为模拟信号显示.由于FFT算法相当于快速卷积,因此频域法的运算速度一般要快于时域法,尤其在压缩比较大的情况下. |

图3 频域法实现数字脉压 合成孔径雷达相关文章:合成孔径雷达原理

相关推荐技术专区 |

评论