利用AMSVF进行混合信号SoC的全芯片验证

UPS求解器

一般来说,电源/地线网络中存在大量的寄生RC,在版图后仿真时,这些寄生RC将会大大降低性能,并侵占大量内存。对于这类模拟,AMSVF中的UPS求解器可被用于加速模拟速度,同时保持精确性。模拟器首先侦测电源网络,然后将整个设计分离为电源网络和信号网络两部分。电源网络部分由UPS求解器处理,而信号网络部分则由Ultrasim求解器处理。电源网络模拟的示意图如图2所示。

图2 电力网络模拟法示意图

使用传统的瞬态模拟和UPS求解器分别进行电压降分析的性能对比如表1所示。

VR技术

由于芯片内电源电压不断降低,并开始采用多电源电压,因此,越来越多的混合信号/RF或数字电路均使用片上稳压器来产生内部供电电压。Ultrasim求解器通过有效的分区技术实现模拟加速,但这只能应用在电路由理想电源电压驱动的情况下。使用传统的分区技术,所有连接到内部稳压源的模块都必须包含在单个分区内,严重影响了模拟速度。

VR(稳压)技术能够克服这种限制, 让用户能够方便地对由内部稳压器供电的电路模块进行模拟仿真。

快速包络分析

总的来说,当被调制电路采用传统的瞬态分析时,需要非常小的时间步长以适应高频载波信号,并且需要长时间的持续周期覆盖低频基带信号,这将使得模拟变得非常缓慢和困难。快速包络分析主要用于解决这个难题,这些电路类型通常出现在发射器、接收器等RF电路中。

AMSVF的快速包络分析功能提供了对模拟/混合信号电路进行模拟和设计的有效方法。任何包含已调制信号的电路或RF部分都可以通过快速包络分析法进行模拟,而电路的其它部分则由数字求解器或传统的瞬态模拟法进行仿真。包括数字和模拟电路在内的所有仿真都在每个时间步长进行同步,它考虑了各仿真之间的耦合,并确保解决方案的精确性。快速包络分析可以跳过时钟周期中的很多时点,减少大量的时间步长数,简化计算量。

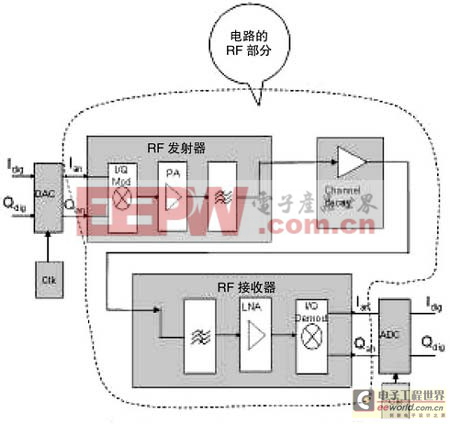

以图3中完整的RF电路为例,它包含了发射器、接收器和ADC/DAC Verilog-AMS模块。与瞬态分析相比,快速包络分析可以通过极小的精确性损失让性能提高7倍。两种方法的波形对比如图4所示,来自快速包络的最后一个波形跳过了很多周期。

图3 完整的RF电路和ADC/DAC行为模块

结语

AMSVF已经被证明是一种针对复杂混合信号电路进行全芯片验证的有效而强大的工具。它不仅提供了灵活的应用模式,还包括更加先进而强大的功能,能够帮助更多的用户在设计的初期阶段发现设计错误,缩短设计周期,实现一次性流片成功。

评论