基于USB通信的FPGA高速数据采集系统

1.3 USB器件

USB接口使用方便,连接简单,但是通信协议很复杂。因此,USB外设必须使用控制器芯片,管理数据通信USB控制器采用集成了8051单片机的CY7C68013A控制器芯片,该芯片遵从USB 2.0规范,有较快的传输速度,是目前比较通用的一种USB控制芯片。

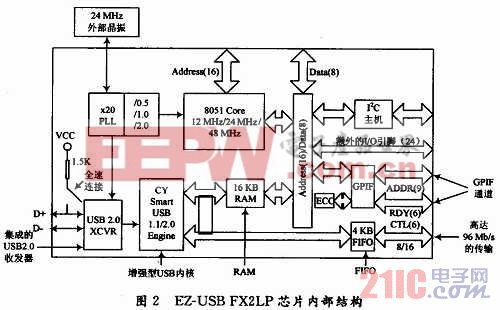

CY7C68013A是Cypress公司EZ-USB FX2LP系列芯片中比较经典的一款USB控制器,其内部结构如图2所示。其中,主要包括USB 2.0收发器、串行引擎(SIE)、增强型8051内核、16 KB的RAM、4 KB的FIFO存储器、I/O接口、数据总线、地址总线和通用可编程接口(GPIF)。本文引用地址:http://www.eepw.com.cn/article/156123.htm

EZ-USB FX2LP拥有非常独特的结构,其串行接口引擎(SIE)负责完成串行数据的解码、差错控制、位填充等与USB有关的功能。串行接口引擎(SIE)能够实现大部分的功能,从而减轻了嵌入式增强型8051的负担,简化了USB固件程序的开发。

2 系统软硬件实现

2.1 A/D转换

系统通过PINFET光电转换为单端模拟信号,而A/D转换器AD7356是差分输入方式,所以需要对输入方式进行转换。AD7356说明书中给出了详细的转换电路,按说明连接即可。由于AD7356供电电源为2.5 V,所以和FPGA之间的连接需要调整AD7356的信号电平,使得输出电平与FPGA的3.3 V电平兼容。在电路设计时,可以通过将AD7356的Vdriver引脚连接到3.3 V,这样使得输出信号电平为3.3 V。

系统采用的AD7356采样频率由输入时钟信号决定,而采样通过使能引脚CS控制。在设定好采样频率后,A/D转换程序主要依靠对CS信号控制,并对输入得两路信号串并转换即可。

2.2 数据缓存

数据缓存主要是利用FPGA内自带的块RAM对多路信号进行排序、存储,然后按USB数据包大小打包传输,因此对于硬件(FPGA)不再多做介绍。

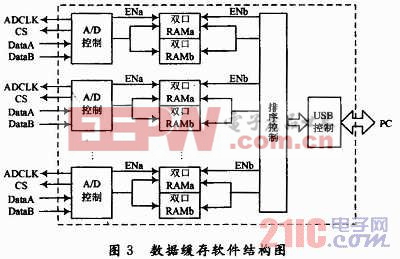

数据缓存的软件实现主要依靠FPGA内的双口RAM IP核。双口RAM由于有2个单独的数据输入和输出口,所以可以调节输入输出端口的速度,使得数据读取与输入速度可以方便的控制。另外,由于本系统有多路光信号,所以FPGA内还需要对各个双口RAM的读取进行控制,对各路信号读取顺序进行,其软件结构图如图3所示。每路A/D都有两个RAM轮流存储采集数据,一方面避免RAM出现数据溢出,保证数据不丢失;另一方面可以通过将RAM大小设定与USB数据包大小一致,使USB传输的控制简单。

评论