CPCI数据总线接口的设计与实现

3 PCI9054局部总线的接口设计

整个CPCI接口的设计思路为:FPGA通过桥接芯片PCI9054与CPCI总线连接,其内部使用异步双口RAM来进行高速数据的缓冲,通过使用VerilogHDL语言编程来控制FPGA中的异步双口RAM,以实现系统数据在嵌入式CUP板卡内存与CPCI板卡之间的高速传输。

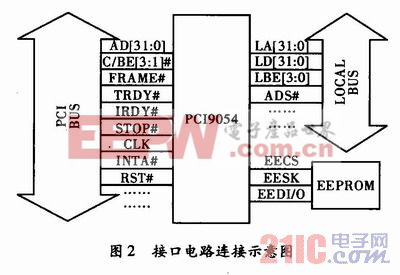

PCI9054提供了3种物理总线接口:CPCI总线接口、LOCAL总线接口和串行EPROM接口。其中CPCI总线接口协议在嵌入式操作系统中的驱动包已经带有,而串行EEPROM的初始化是由PLX公司的PLXMON软件在嵌入式操作系统中进行在线烧写的,所以本系统设计的重点就是关于LOCAL总线接口的控制和传输,其接口电路示意图如图2所示。本文引用地址:http://www.eepw.com.cn/article/156072.htm

PCI9054与本地总线之间的接口称之为LOCAL BUS,是CPCI总线系统设计中十分重要的一环。PCI9054 LOCAL BUS在系统设计中,其总线直接与Alter公司的EP2S90F78014芯片的数据总线相连,同时通过运用Verilog HDL语言编程来实现对双口RAM控制器的功能。

PCI9054 LOCAL BUS有3种工作模式,分别为M、J和C模式。M模式是专为Motorola公司开发和设计的,而另外两种工作模式就应用的比较广泛。其中J模式因为没有LocaL Master,所以它的地址总线和数据线没有分开,从而增加了开发难度。而在C模式下,PCI9054芯片通过片内的逻辑控制可以将CPCI的局部地址和数据总线分开,从而有效地降低了开发难度,并且能灵活地为本地工作时序提供各种工作方式,所以本系统设计方案选择了LOCAL总线的C工作模式,工作频率为40 MHz。

4 局部总线的实现

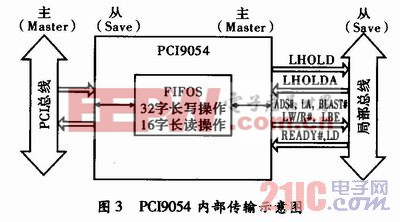

PCI9054支持主模式、从模式和DMA传输方式,根据本系统设计的需求,采用从模式传输方式,即允许CPCI总线上的主设备访问局部总线上的配置寄存器或内存,支持多种模式传输。如图3所示。

评论