TMS320TCI6618-TI 高性能LTE物理层解决方案

算法的信号处理开销,能够支持双通道20 MHz、300 Mbps 下行链接、150 Mbps 上行链接的2x2 多输入多输出(MIMO) 解决方案。此外,与3G 系统相比,LTE 还可使用OFDM 和上下行链路多输入与多输出(MIMO) 技术实现显著的性能提升。

LTE 使用OFDM 支持无线电广播传输,从而能够提供稳定的传输机制来避免恶劣信道条件下的性能衰减、窄带同频串扰、码间干扰和衰减。此外,其还可提供对时间同步错误的高频谱效率及低灵敏度。

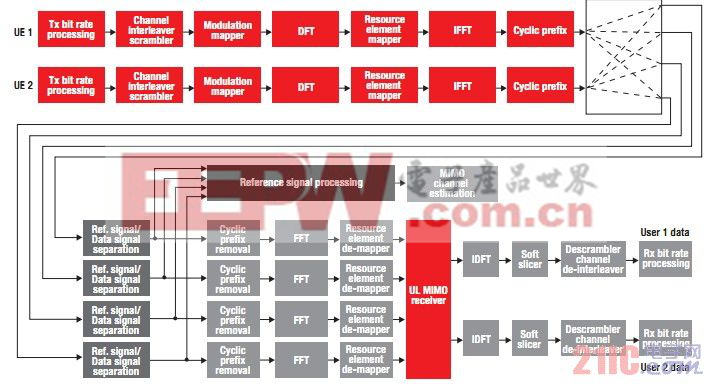

LTE 下行链路处理使用带循环前缀的多载波OFDM 传输方式。在上行链路,带有循环前缀的宽带单载波OFDM 传输能够大幅减少所传输信号的瞬时功耗变化。快速傅里叶变换(FFT)能够为OFDM 调制解调提供低复杂度的高效率实施方案。

图2LTE MIMO 信道模型为了提升性能,LTE 同时在发送器和接收机中都采用了使用MIMO 天线的智能无需额外增加带宽或发送功率就能显著提高数据吞吐量并扩大频率覆盖

多天线上行链路MIMO 接收机技术能够有助于提高信噪比。在接收机主要受噪音损害时

最大比合并(MRC) 是一种非常有效的天线合并策略。在干扰幅度非常强的信道条件下,最小均方误差(MMSE) 结合技术是确定最小化均方误差的天线加权矢量的极佳方案。MMSE

MIMO 均衡的浮点实施可显著减低计算复杂度,并实现极高性能,从而成就了高效率的

LTE MIMO 接收机。

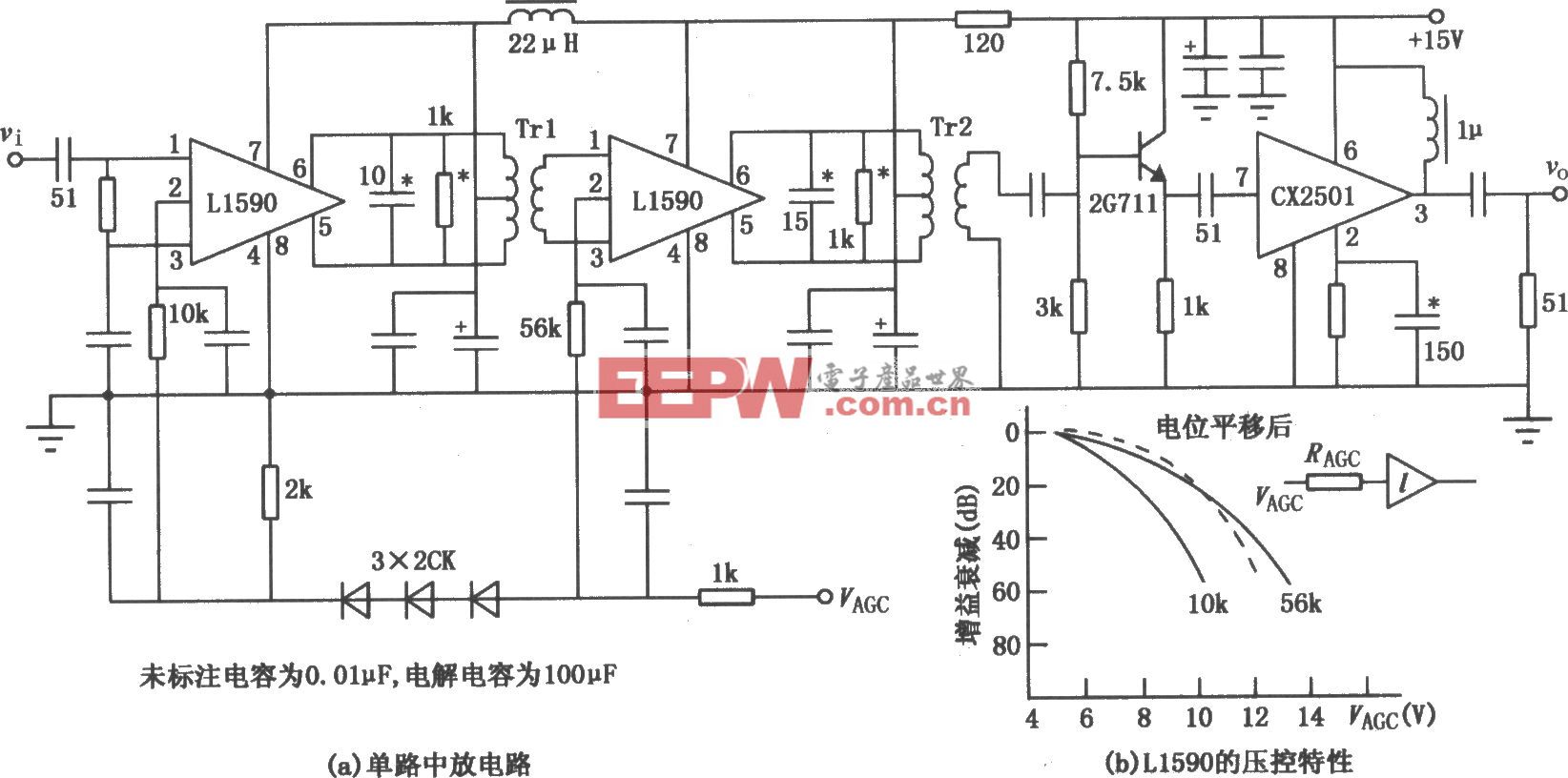

LTE 推动器 TCI6618 SoC 是TI TMS320C66x DSP 多内核系列成员。其基于TI 最新的KeyStone多内核架构之上,适用于高性能的无线基础局端应用,是用以应对LTE 设计挑战的完美方案。图3 阐述了该器件的特性和处理组件。

TCI6618 针对LTE 的多内核架构在业界率先提供了一种可将精简指令集计算机(RISC)和DSP 内核同专

主要特性 用协处理器和I/O 高度集成在一起的高性能结构。此外,KeyStone 也是业界第一款能够为所有处理内核、外设、协处理器以及I/O 提供足够内部带宽以实现非阻塞、零延迟接入的多内核架构。这主要得益于4 种硬件的支持,如多内核导航器、TeraNet、多内核共享存 储器控制器及超链接。多内核导航器是一种基于分组的创新型管理器,能够对8,192 个队列进行控制。当向向各队列分配任务时,多内核导航器可提供硬件加速的调度,以直接将任务指向相关的可用硬件。基于分组的SoC 可使用2Tbp 容量的TeraNet 交换中心资源进行分组传输。多内核共享存储器控制器能够在无需耗用容量的情况下允许处理内核直接访问共享存储器,因而能够避免因存储器接入造成分组传输的延迟。超链接可提供50 Gbps 的芯片级互连,使SoC 能够协同工作。其极低的协议开销和高吞吐量特性使超链接成为芯片对芯片互连的理想接口。超链接与多内核导航器协同工作,可将任务透明性地分派给串联设备,而且执行这些任务就如同在其本地资源上运行一样。

C66x 内核TCI6618 具有四个支持定点与浮点运算操作的1.2-GHz C66x 内核。其可提供1.2条件下每秒153.6 GMAC 的定点运算性能以及每秒76.8 GFLOP 的浮点运算性能。指令集架构新增了90 条全新的高性能指令,尤其是浮点指令与矢量信号处理指令,从而能够支持16 位数据的双路单指令多数据(SIMD) 操作以及8 位数据的四路SIMD 操作。该款超长指令字架构可支持8 个同步问题,并为复数计算和矩阵处理进行了优化。其具有更低时延的浮点能力与对MAC 性能的4 倍速增强,不仅显著加速了LTE MIMO 的均衡,同时还提高了LTE 所需的大部分DSP 处理能力。

评论