一种基于稀疏矩阵的多核并行扰码方法

摘要:针对多核环境中高速无线信号的加扰、解扰,提出了一种基于稀疏矩阵的多核并行扰码方法。首先对输入信号进行串/并转换,并将各路信号分别送入对应的处理器核;考虑基于稀疏矩阵的并行扰码生成器,在单个处理器核内,将其生成的伪随机码与输入信号进行模二加运算,得到单路信号的扰码输出;最后将多路并行的扰码输出变换为串行输出。运算量分析结果表明,采用IEEE 802.11n中的扰码生成多项式,与普通矩阵乘法实现的多核并行扰码方法相比,基于稀疏矩阵的多核并行扰码方法,其运算量降低了一个数量级。

关键词:稀疏矩阵;多核;并行扰码;运算量

0 引言

无线通信速率的不断提高,要求无线通信设备的处理速度不断提高。未来无线通信设备处理速度的提高不仅依赖于单处理器处理速度的提高,更主要是依赖于片上处理器核数量的增加。因而,多核处理器被广泛应用在无线通信信号处理中。

加扰、解扰是无线通信信号处理中的重要环节。随着无线通信速率的提高,串行扰码对硬件处理速度的要求越来越高。针对高速信号的加扰、解扰,串行扰码不再适用。因此,文献提出了矩阵法实现的并行扰码方法,首先将串行的高速信号转换为并行的低速信号,再利用扰码生成器产生的多个并行相位,同时对输入并行信号进行扰码处理。其中,扰码生成器是基于线性反馈移位寄存器的状态转移矩阵实现的。文献提出了用查表法实现的并行扰码方法,并行扰码的步骤与文献一致,但其扰码生成器是基于伪随机序列存储表实现的。与用矩阵法实现的并行扰码方法相比,该方法的运算量小,存储量大。文献改进了并行扰码方法的FPGA结构,在该结构中,各路并行扰码输出的路径时延均仅由一个D触发器和一个异或门构成,该结构对高速信号处理具有很强的适应性。在文献的基础上,文献进一步改进了并行扰码的FPGA结构,

与文献的结构相比,在保证输出路径时延不变的条件下,该结构减少了寄存器的使用数量。

针对多核环境中的高速无线信号,本文提出一种基于稀疏矩阵的多核并行扰码方法。该方法应用稀疏矩阵的存储及运算,产生了并行输出的伪随机码,并实现了多核的并行加扰、解扰。

1 系统模型

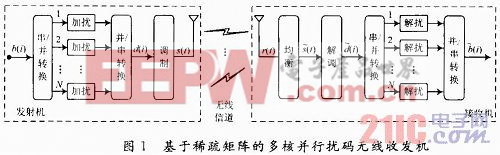

基于稀疏矩阵的多核并行扰码无线收发机通信链路如图1所示。发射机对比特流b(i)进行基于稀疏矩阵的多核并行加扰,具体步骤为:首先对输入信号进行串/并转换,将N路信号分别送入对应序号的处理器核,在单个处理器核内,对输入信号进行加扰处理;然后将N路并行扰码输出经过并/串转换得到d(i)。d(i)经过调制,产生发射信号s(t)。发射信号经过无线信道到达接收机。接收机对接收信号r(t)进行信道均衡,得到发射信号s(t)的估计值![]() ;然后解调得到比特流d(i)的估计值

;然后解调得到比特流d(i)的估计值![]() ;最后经过基于稀疏矩阵的多核并行解扰恢复出比特流b(i)的估计值

;最后经过基于稀疏矩阵的多核并行解扰恢复出比特流b(i)的估计值![]() 。多核的并行解扰步骤与加扰步骤类似,这里不再赘述。

。多核的并行解扰步骤与加扰步骤类似,这里不再赘述。

评论