通信系统中Viterbi译码的Matlab仿真与实现

2 维特比译码原理

Viterbi译码是卷积码的最大似然译码算法,是一种实用化的概率算法。它的基本思想是把已接收序列与所有可能的发送序列作比较,选择其中码距最小的一个序列作为发送序列。从图2的卷积码网格图可以看出,卷积码编码过程就是编码器状态沿着时间轴的一个转移过程。Vi terbi译码则是在如图2所示的网格图上搜索最可能的状态跳转路径,设(n,k,m)编码器输出的码序列为T,寄存器长度为L,经过离散无记忆通道(DMC)传输后送入译码器的序列是R=T+E,其中E为信道的错误序列。译码器根据接收序列R,按最大似然译码准则找到接收序列在如图2所示的编码器网格图上所走过的路径,这个过程就是译码器计算和寻找最大似然函数的过程,或者说是寻找最大度量路径的过程。其中最大似然函数为

寻找最大度量路径时首先要在t时刻读取所有状态的幸存路径度量值,再根据t+1时刻的输入算出跳转路径的度量值,将t时刻的幸存路径度量值和t+1时刻的跳转值相加,可得到t+1时刻到状态S的幸存路径度量值。这样每个状态都有一个幸存路径,根据这些幸存路径和最终编码器所处的状态就可以得到编码器的状态转移路径即译码结果。

3 维特比译码实现

维特比算法是将接收到的信号序列和所有可能的发送信号作比较,选择其中汉明距离最小的序列作为现在的发送信号序列。译码一般由图2所示的网格图中的S0状态开始,由于有6个寄存器,当每个寄存器的值都为已知时再输入才能得到唯一的编码器输出,所以译码初期连续接收12 bit的信息,它是由6 bit的输入得来的,由于6 bit的输入有64种可能的输出,所以将接收到的12 bit与64种可能相比对找出汉明距最小的一组即为想要的编码器输入也即译码器的输出。

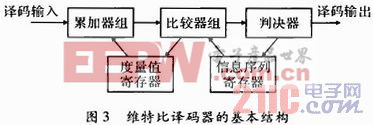

一个完整的译码器一般包括以下7部分:状态发生器、累加器、比较器、度量值寄存器、信息序列寄存器、判决器、其他控制电路等,如图3所示。本文引用地址:http://www.eepw.com.cn/article/155065.htm

对于(2,1,7)卷积码,在一个译码周期内,累加器完成64条支路度量值计算,比较器组完成同一状态的路径距离值比较,将较小者存入64个度量值寄存器。判决器选出64个信息序列寄存器中的最小者,并将相应信息序列寄存器的译码结果输出。

当确定各寄存器的初值后,从当前状态经过加比选蝶形运算后,到达下一状态,通过对每一分支度量的累积计算,经比较分析找到与接收序列距离最近的幸存路径。程序中的Nextstaterow是经过加比选得到的下一状态,将每次加比选的结果Nextstaterow保存下来放在一个数组Nextsatate中,当译码完成后Nextsatate中的各值即为译码所走过的路径,按照Nextsatate中的值,通过如图2所示的网格图回溯即可得到译码结果。

在信息传输的过程中,由于各种噪声的影响会造成接收到的数据有可能是误码,但连续出现2 bit的误码的概率又非常小,所以这里只考虑出现一比特误码的情况。当出现误码时两条岔路汉明距相等,由于基本不会出现2 bit的误码所以等到下一个节点时判断汉明距的大小就可以找到正确的输出。

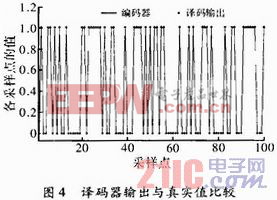

图4是译码输出与编码器输入的比对,误码率很低,在所截取的图片中无误码出现,由仿真结果可清楚地看出译码器的输出与编码器的输入完全重合,说明译码器具有良好的前向纠错功能,用于通信系统可以提高信息传输的可靠性。

4 结束语

验证了Viterbi译码方案的可行性,这种译码方法得到的输出误码率可低至10-6。这种方案已用于某导航系统中,经测试,该译码方案在低信噪下也能达到较低误码率。

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论