扩频通信系统CCSK信息调制解调算法设计

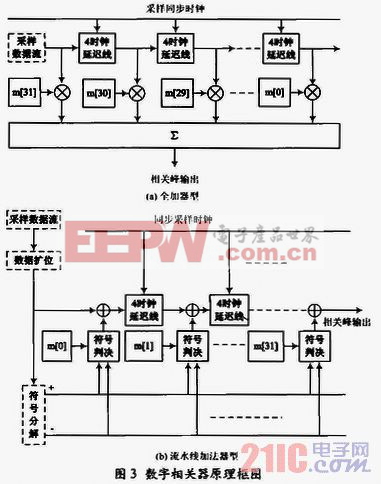

数字相关器是CCSK信息解调的关键部件,通过相关器进行CCSK信息解调有两种不同的逻辑电路架构,包括两级串联型相关处理算法电路和多极并行数字相关器。无轮哪种CCSK相关解调器,其核心都是数字相关器,而数字相关器分为全加器型数字相关器和流水线加法器型数字相关器。这两种数字相关器的原理框图如图3所示。

两级串联型CCSK相关解调逻辑电路一般由两个全加器型数字相关器级联而成。如采用32 bit m序列扩频码的系统,可将两个32 bit相关器级联成64 bit相关器,其m序列本地码可设置成两个同样的m序列:

{a31,a30,a29,…,a2,a1,a0,a31,a30,a29,…,a2,a1,a0}

当输入基带码流信号为m序列的某一种32 bit循环移位码时,相关器就会输出相应的相关峰信号。其过程如下:

输入基带码流为32 bit m序列的原码时(时间次序为{a31,a30,a29,…,a2,a1,a0}),当码流与第一段本地码对应缓冲器内的本地序列{a31,a30,a29,…,a2,a1,a0}一致时,相关器就会输出第一相关峰;在采样同步时钟的驱动下,输入码流进入第二段本地码对应缓冲器内,此后,当码流与相关器的本地序列{a31,a30,a29,…,a2,a1,a0}一致时,相关器就会输出第二相关峰。

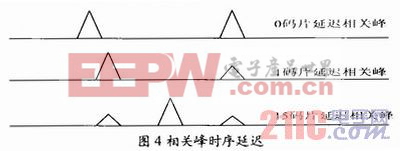

当输入信号是扩频码m序列的1次循环移位码时,只有当输入码流信号被驱动到{a30,a29,…,a2,a1,a0,a31}的位置上时,相关器才输出相关峰信号。相对于0次循环移位码产生的相关峰,其时序延迟了一个码片单位。依次类推,当输入信号是扩频码m序列的N(0≤N≤31)次循环移位码时,通常可以得到延迟N个码片时间的相关峰。图4所示是相关峰时序延迟示意图。

通过计算相关峰输出时间同基准(0延迟)相关峰之间的时间差,可以提取调制在信号上的信息数据N:

N=(数据相关峰字符时间-基准相关峰字符时间)/码片时间

采用两级串联型CCSK相关解调逻辑电路解调CCSK信息消耗的硬件资源较少,但由于要对相关峰进行定时检测以及消除部分相关峰,因此,对电路的处理时序较为严格,只能采用全加器型数字相关器来实现。而流水线加法器数字相关器由于不具有实时归零功能,无法实现两级级联,因此不适合两级串联型CCSK相关解调逻辑电路的相关器。

通信相关文章:通信原理

评论