小型化低功耗数字信号处理器设计

由于大量的分布式RAM是构成数字延迟线的理想硬件资源,因此,通过RAM构建数字信号延迟线不仅可以大量节约宝贵的LE资源,同时也可以使设计软件的布线难度大大降低、信号的传递延迟减小,并使系统信号处理速率的裕度提高,有利于满足系统对工作环境的适应性要求。此外,同样功耗下,大量采用RAM实现信号处理算法的效率最高。如扩频通信系统中重要的数字信号处理部件——数字相关器,其主要电路构建就是数字延迟线。实现数字相关处理时,数字延迟线至少能够存储4倍扩频码长度的数据。以20 Mbps BPSK信号的系统为例,若其同步信号段采用64 bit的扩频码,要实现对每个输入扩频字符进行相关处理,就必须采用256级数据延迟线输入对数据码流进行存储。如果输入码流的位宽为16 bit,则仅实现一条延迟线就至少消耗4 000个LE资源,对于采用正交方式的信号处理算法,实际上需要对I、Q两路数据流进行

存储,因而需要8 000 LE,这对于FPGA是一个不小的开销,而采用RAM资源,则所占全部资源的比例极小。

ALTERA的ARRIA系列FPGA的另一个重要特点是其垂直可移植性非常好,同样封装的芯片具有较大范围的不同容量可互换性,也就是说,在不改变任何硬件电路板的前提下,小规模芯片可直接替换大规模芯片。因此,采用该系列芯片在设计的初期可以选用规模较大的芯片,当完成设计后,可以根据实际的硬件资源消耗情况重新选择同系列中的小容量FPGA。这种高度灵活性不但保证了信号处理器算法由于资源消耗不确定性所带来的选型困难,同时可为最大限度地降低功耗提供一条可行的路径。

在该数字信号处理系统中,数字上变频器也是数字信号处理的一个关键。如果采用单纯的D/A来产生100 MHz中频调制波形,至少要以4倍以上的信号输出速率来产生相应波形,这给FPGA的信号数据传输带来了较大困难。若采用FPGA高速收/发器实现上变频码流的输出,系统功耗又会大幅提高,不利于功耗的降低。而如果采用AD9957,则可以通过其正交方式或单音频方式产生高质量中频调制波形,而其总功耗比

其他设计方案要低,同时可大大简化波形产生难度。

除了上述主要的数字处理器部件外,该数字信号处理系统还在保证性能的前提下,大量采用了多种低功耗的数字芯片,包括DSP、RS422/485接口等。同时,许多接口处理时序逻辑均嵌入FPGA内实现,因而精简了电路,并使独立芯片的某些不需要的功能得以裁减,从而使电路得到优化,也从总体上降低了功耗和电路的规模。

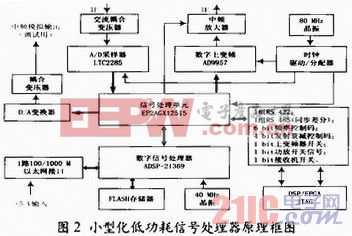

基于上述小型化、低功耗设计方法途径构建的高性能、高集成度、低功耗数字中频通信信号处理系统的原理框图如图2所示。经实际测量,该系统存全速工作下的整板功耗为9 W,远远小于12.5 W的设计指标。

3 结语

对于数字信号处理系统,最好的设计方案就是在实现基本功能和性能的前提下,将全部的功能部件集成在一个芯片内,包括信号处理算法电路、接口电路、定点/或浮点DSP、微控制器,甚至是高性能的A/D和D/A在内。这样的数字处理系统称为SoC、(片上系统),其主要特点是集成度高、功耗低、资源最优、处理速度快、信号延迟小。具有上述优点的SoC是实现小型化、超低功耗数字信号处理系统的重要技术于段,也是实现信号处理领域的前瞻性发展趋势。

受半导体工艺水平的限制,目前尚无法将诸多数字处理功能集成在单一的芯片内,尤其是高速A/D采样器这种同时具有数字和模拟两种电路特性的功能部件以非独立部件植入可编程逻辑器件内时,其技术难度仍然较大,因此,要实现真正意义上的片上系统,还有许多技术难关需要攻破。尽管如此,业界已经在SoC的技术道路上向前突进了一大步,ALERA公司推出的内嵌ARM处理器和浮点协处理器的28 nm工艺FPGA即将推出,若通过该系列FPGA构建通信信号处理系统,可以使原先必须的DSP+FPGA的基本电路构架,简化成单一的FPGA电路构架,从而较大程度上降低了功耗和电路面积,使信号处理器小型化向前迈进一大步。

评论