基于SOPC技术的异步串行通信IP核的设计与实现

3 UART IP核设计

3.1 PLB Slave Single模块介绍

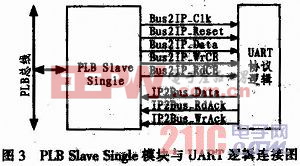

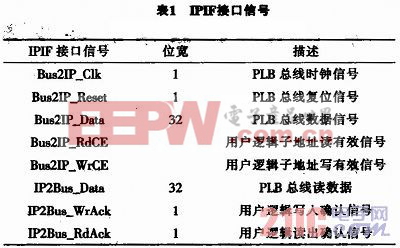

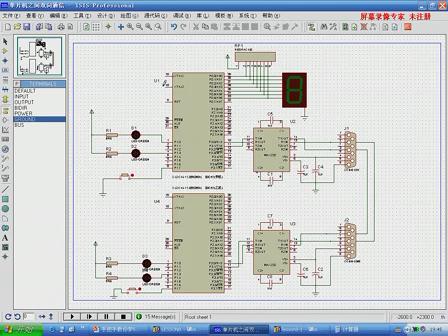

如上,UABT IP核作为PLB总线的从设备,必须提供PLB总线接口。但由于PLB总线协议复杂,实现其接口难度较大,Xilinx公司为了使用户编写的逻辑能够方便的连结到PLB总线上,提供了一种PLB总线与用户逻辑之间的接口模块(IPIF,IP Interface),利用它简化了PLB总线接口信号、总线协议和其他接口相关问题。IPIF接口逻辑中最简单的模块称为PLB Slave Single模块,它提供了一种轻量级的PLB总线接口,为PLB总线主设备提供了解析从设备地址空间,读写从设备寄存器/存储空间等基本服务。本文设计的UARTIP核与MicroBlaze处理器之间仅通过寄存器的读写进行交互,PLB Slave Single模块很好的满足了该设计要求,因此采用PLB Slave Single模块与UART逻辑共同构成了UART IP核。PLB Slave Single模块与UART逻辑之间的连接关系如图3所示,接口信号说明如表1所示。本文引用地址:http://www.eepw.com.cn/article/154802.htm

在系统中,UART IP核的内部寄存器组映射为处理器的某段地址空间,MicroBlaze处理器通过对该段地址的读写实现对UART IP核的访问。当MicroBlaze处理器访问UART IP核的某个寄存器时,PLB总线会产生相应的地址信号和读写信号,该信号被UART IP核中的PLB Slave Single模块解析并生成相应的IPIF信号,UART IP核中的UABT逻辑响应该IPIF信号,完成寄存器的读写。

3.2 UART IP核寄存器组设计

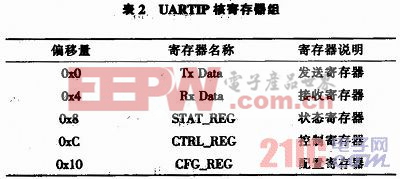

文中设计的UART IP核提供了5个寄存器,如表2所示。其中发送寄存器和读接收寄存器完成UART数据的发送和接收。状态寄存器提供了UART IP核内部状态,包括接收数据有效,发送FIFO满,接收FIFO满,奇偶校验错等状态。控制寄存器提供了UART IP核复位功能。配置寄存器提供了波特率设置,奇偶校验位设置等功能。

3. 3 UART协议逻辑模块设计

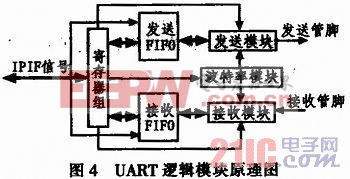

本文设计的UART协议逻辑模块主要包括波特率产生模块,发送模块,接收模块,寄存器组等几个部分,其结构如图4所示。寄存器组说明如表2,其他几个模块的设计如图4所示。

评论