基于SOPC的脑电信号实时处理

2 SOPC硬件结构

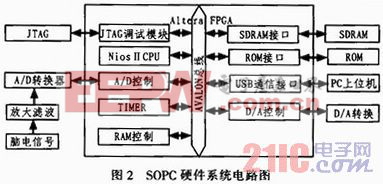

文中的核心控制芯片采用ALTERA公司的CycloneⅡ系列型号为EP2C8020818N的FPGA芯片。该芯片有8 256个逻辑单元,内置18个嵌入式18x18乘法器,2个PLLs,完全满足本设计的需要。此系列芯片支持NiosⅡ32位嵌入式软核处理器,该处理器系统包括一个可配置NiosⅡCPU软核、与CPU相连接的片内外设和存储器以及与片外存储器和外设相连的接口等。所有组件在一个FPGA芯片上实现。SOPC硬件系统结构如图2所示。本文引用地址:http://www.eepw.com.cn/article/154471.htm

整个系统以NiosⅡ软核处理器为主,Avalon总线为核心,各个外设端口挂接在Avalon总线上。通过Avalon总线,NiosⅡ主设备控制各从设备。Avalon总线支持多个总线主外设,允许在单个总线事务中在外设之间传输多个数据单元。这一多主设备结构为构建SOPC系统提供了极大的灵活性,并且能够适应高带宽的外设。

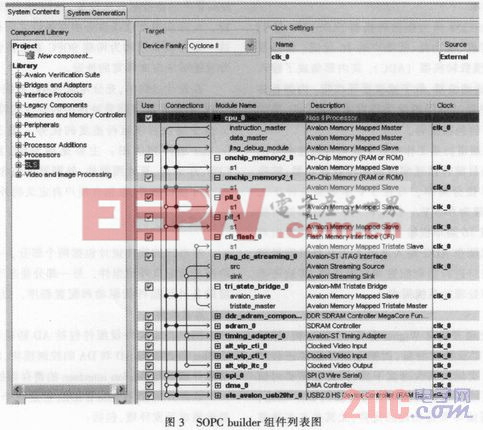

在设计过程中,充分考虑SOPC系统的特色,充分发挥了SOPC系统在数字信号处理中的并行运算优势和NiosⅡ自定义指令加快程序运行速度的优势。图3为本系统的SOPCbuilder组件列表图:主要是用SOPC Builder选取合适的CPU、存储器、及外围器件,外围器件包含系统自带的如定时器,SPI接口核等,也包含用户自定义的外设组件(AD,DA)。

评论