基于FPGA的通信接口模块设计与实现

2.3 状态数据处理逻辑

由于各个前端受控模块下行数据量较少、数据间时间间隔较大,而FPGA内部数据处理速度远快于外部接口,因此不存在某一受控模块始终占据总线的情况。这样不需要考虑按照请求到来时间顺序进行处理请求,而是状态数据处理逻辑接到受控模块接口的总线请求后,按照固定的优先级处理。

2.4 三线制同步串行口

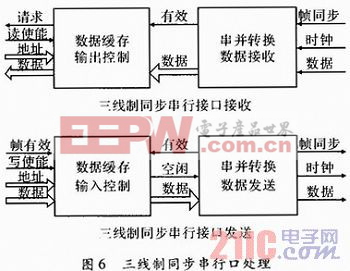

三线制同步串行接口的逻辑结构如图6所示。三线制同步串行口接收模块可分为数据接收和数据接收缓存两部分。数据接收部分由移位寄存器组成。移位寄存器受接收的时钟信号控制,实现串并转换,数据接收完成后,直接输出到数据接收缓存。数据接收缓存设置2级异步FIFO,实现跨时钟域变换。当缓存中有数据时,向状态信息处理模块发出请求,等待读出数据。本文引用地址:http://www.eepw.com.cn/article/154067.htm

三线制同步串行口发送模块同样可分为两部分:数据发送缓存和数据发送。数据发送部分主要是由移位寄存器、移位计数器组成。根据不同的数据长度设置不同长度的移位寄存器,实现数据的并行输入和串行移出。移位计数器控制数据移出的个数,同时控制时钟信号和帧同步信号的产生。数据缓存部分根据传输数据的不同而不同。对于周期性控制命令设置一级缓存,当新数据来时缓存被新数据覆盖。对于非周期控制命令设置4级FIFO,由于非周期控制命令较少,4级缓存已经足够。数据缓存部分优先发送非周期控制命令。

评论