寄生电容--用在多支路总线上的连接器简介

本文引用地址:http://www.eepw.com.cn/article/154021.htm

2、电路走线电容

根据走线的阻抗和传播延时,采用下式可以计算每英寸长度电路走线的电容:

其中:TD=走线传播延时,PS/IN

ZO走线阻抗,Ω

C=电容,PF/IN

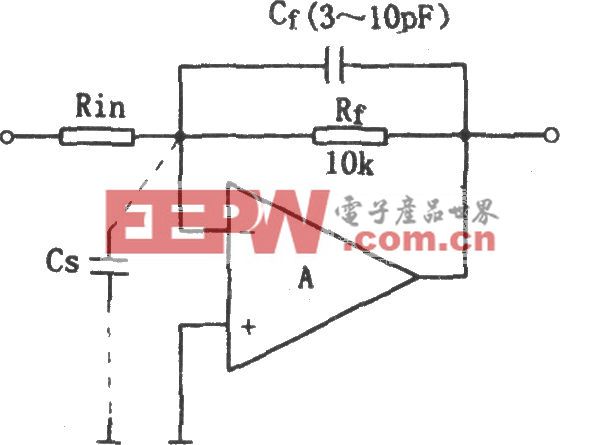

3、接收器和驱动器电容

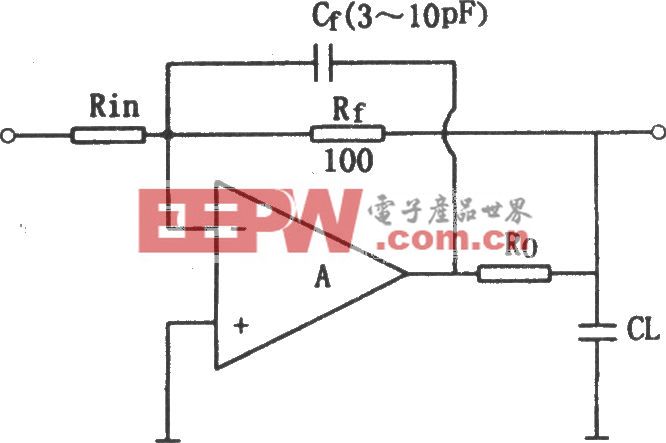

在很多高速接收器的技术规范文档中,生产商说明了其电容参数。但是,如果没有技术规范文档,可以采用图1.6所示的电路测量其中一个样品。测量时,调整脉冲发生器产生一个脉冲,使其电压大小处于接收器有效范围的中间,而且幅值和实际应用条件下的幅值相差不多。给接收器上电。一般典型的电容值为2~10PF。

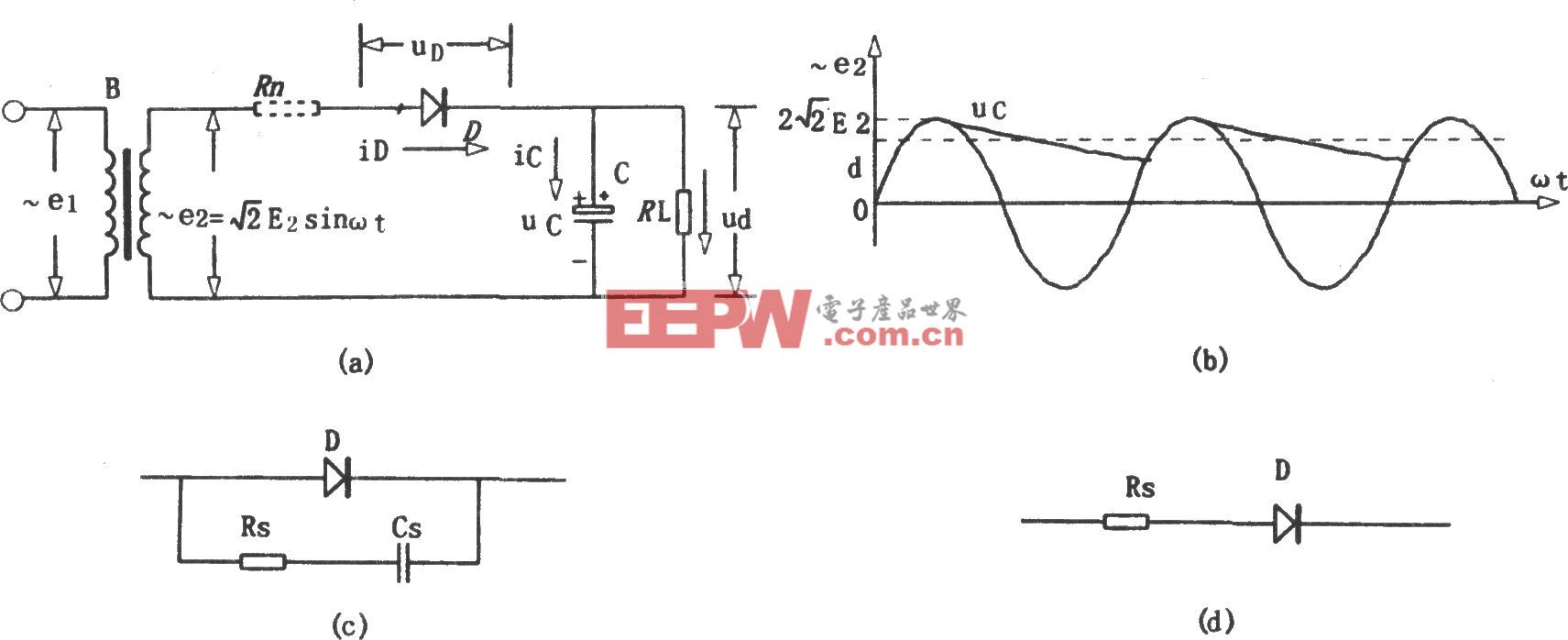

一个三态驱动器在处于关闭状态时的电容是很大的。很多生产商不提供这个电容参数,希望用户忽略这个因素。实际上驱动器由很大的晶体管组成,当其关闭时具有非常大的寄生电容。

只有通过测量的方法才能得到驱动器的实际电容,采用的是与接收器相同的测量方式。发送门加上电源,但其输出使禁止,使脉冲发生器偏置在门电路的有效范围。测量值一般不会高于80PF。

例:走线电容

一条内部走线,从连接器引出,首先进入一个驱动芯片,然后到一个接收器,总长0.75IN其电容是多少?

TD=180PD/IN(FR-4内部走线)

ZO=50Ω

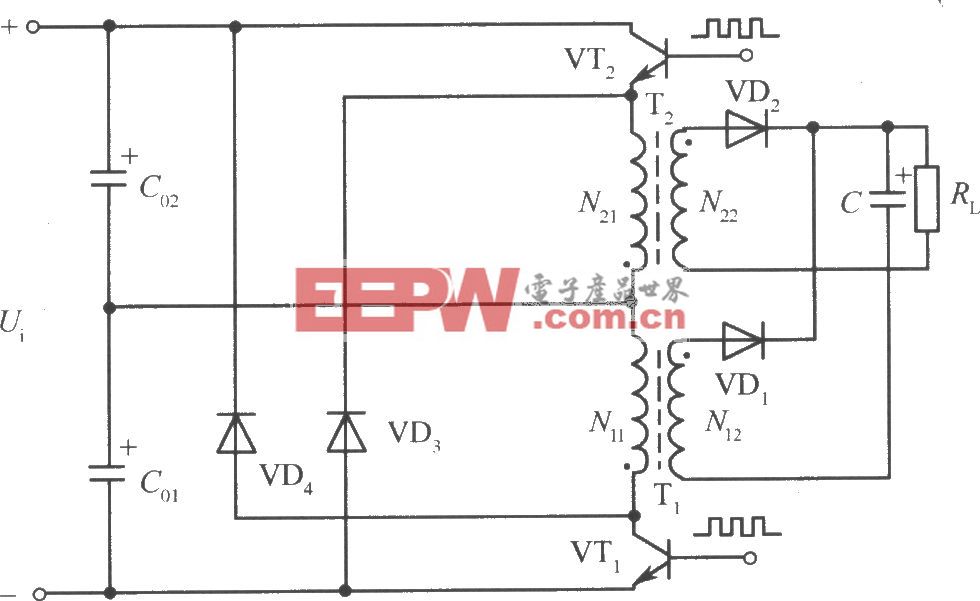

4、均匀间隔负载

电容集中到一点相比,对于信号的传播,间隔均匀地布放总线分支点,可以减小总线阻抗,降低干扰的影响。

在一个插板式的机架系统中,如果插槽沿着母板卡均匀安置,并且每个板卡都插在插槽上,这时的均匀间隔模型是适用的。如果系统工作时有些插槽总是空的,均匀间隔模型将不再适用。

有一种折衷模型的假定连接器的电容在每个插槽中,但没有插卡。只有连接器电容的作用对降低背板的阻抗、降低传输速度的影响是显著的。降低背板的阻抗带来一个好效果:当插入每块板卡时,对整个传输特性的影响很小。

5、低速总线

如果不需要很高的速度,可以在多支路总线中考虑源端端接。这种情况下可以省略图9.9中总路线两端的电阻,通过一个串联衰减电阻把每个三态输出连接到总线上,接收端可以直接连到总线上。在插板式的机架应用中,这种拓扑结构的铖点在于,在背板上不需要端接元件。

如果驱动器的上升时间比总的电气长度长,总线作为一个集总电路元件,因此没有反射。源端电阻给总线的集总电容充电,虽然缓慢,但却是正常的方式。

如果驱动器的上升时间和总线的电气长度相当,总线上会出现反射。我们可以减缓驱动器的上升时间,直到总线考虑不周为一个集总电路,从而减少反射。通过使源端电阻大于总线阻抗,就会得到RC上升时间的效果,随着阻抗的增加,系统达到一个慢的单调的RC上升特性。连接器的电容,以及其他走线和驱动端或接收端电容,都通过源端电阻缓慢地充电。

如果可以提供等待,总路线在每个时钟之间稳定下来,那么就可以采用一个大的源端电阻,从而具有以下优点:

降低功耗,静态驱动电流为零

简单,背板上不需要端接电阻

降低EMI,减少了渡过连接器的电流

电容的相关文章:电容屏和电阻屏的区别

评论