电力线载波通信的外围电路设计

3 串口接口和电源电路设计

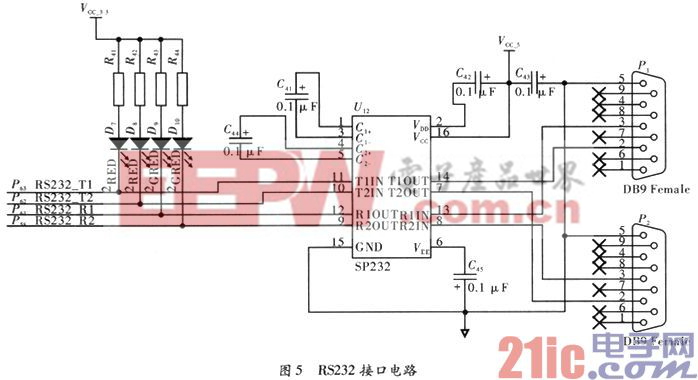

由于RS-232-C标准所定义的高、低电平信号与一般的LVTTL电路所定义的高、低电平信号完全不同,LVTTL的标准逻辑“1”对应2~3.3 V电平,标准逻辑“0”对应0~0.4 V电平,而RS-232-C标准采用负逻辑方式,标准逻辑“1”对应-5~-15 V电平,标准逻辑“0”对应+5~+15 V电平,两者间要进行通信必须经过信号电平的转换。系统使用串口进行调试,串口的信号电平是5 V,而FPGA输出电平最高是3.3 V,因此,两者的信号需要电平转换,可用一块MAX232来满足4路的电平转换。RS232接口电路如图5所示。本文引用地址:http://www.eepw.com.cn/article/153687.htm

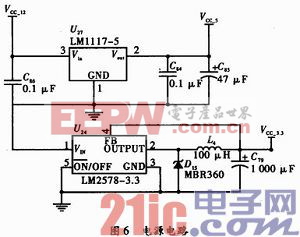

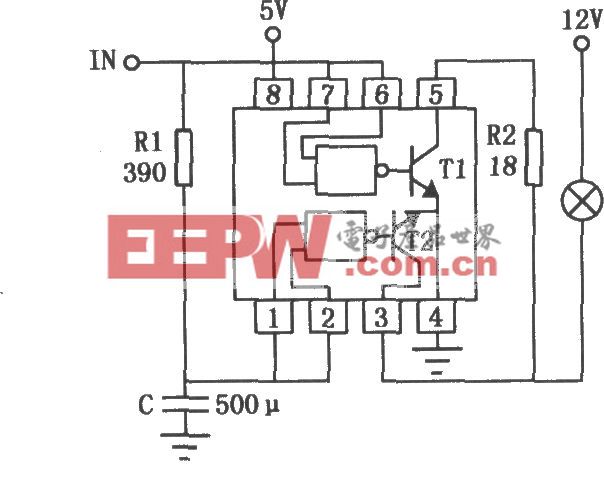

在整个电力载波扩频通信系统中,放大驱动、耦合电路和AGC使用了12 V电源,AD7822和MAX232的工作电平是5 V,时钟振荡器的工作电平是3.3 V,所以需设计一套多电源供电的方案。如图6所示,12 V电源直接由变压器产生,5 V电源用LM1117芯片实现,3.3 V电源由LM25 76匹配获得。

4 硬件抗干扰措施

系统的稳定性是实现其功能的前提。在本系统中,因为需要耦合到220 V的电力线上,因此,元件的布局、布线以及电源、地线的处理都将影响电路性能和电磁兼容性能。

结合实际遇到的干扰情况,本系统的硬件抗干扰措施主要集中在如何提高PCB板的抗干扰性能上。主要采取了以下几种抗干扰手段:

(1)抑制干扰源。1)在布板时让电容、电感的引线尽量短。2)电路板上各个IC都并接了一个0.01~0.1μF高频电容,以减小IC对电源的影响,并且高频电容的布线、连线靠近电源端并尽量粗短,以免增大电容的等效串联电阻,影响滤波效果。3)布线时都采用45°折角,尽量减少90°折线,以减少高频噪声发射。

(2)切断干扰传播路径。1)充分考虑到电源对系统的影响,采用纹波系数小的电源管理芯片进行设计,并给FPGA芯片电源加了滤波电路以减小电源噪声。2)布线时使晶振与FPGA芯片引脚尽量靠近,用地线隔离时钟区,将晶振外壳接地。3)大功率器件都布线于电路板边缘,尽量减小它对其他电路的影响。4)在PCB板子上下两面进行大面积铺铜并接地,以屏蔽电磁干扰。

(3)提高器件抗干扰能力的处理。1)布线时尽量减少回路环的面积,以降低感应噪声。2)加粗电源线和地线的布线以减小压降、降低耦合噪声。3)IC和FPGA芯片闲置的I/O口,都予以接地或接电源。4)IC器件多采用贴片,而不是采用分布电容较大的DIP封装。

此外,在PCB内部处理数模共地的问题时,将板内部数字地和模拟地隔离,只是在PCB与外界连接的接口处,数字地与模拟地使用一个0 Ω电阻短接。

5 整机功能测试结果分析

最后把外围电路和调制解调芯片组合起来进行整机功能测试:(1)不带电导线测试。接收端能准确接收到发送信号,并将发送的数据准确显示出来,接收端和发送端具有基本的通信功能,设计方案在整机实现上可行。(2)双机低压变压器小区内测试。在短距测试时,一开始不能正常接收,于是更改了门限值,反复测试后可达到正确接收。

在双机小区内测试时。发现当距离较大时,偶尔会有误码。这是由于随着距离的拉长,引入了更多的干扰,必然有多经现象发生,因此信号能量有所损失;同时接入点有较大的阻抗,对信号也会有衰减,同时发现在晚上,因用电设备减少,负载减轻,干扰减小,通信效果会比白天好。当加入CRC纠错冗余编码后,可以有效的消除误码率,实现正确接收。由于PN码不长,捕获时间一般较短,在一个PN码周期内便可实现。

经过测试,在信噪比为-20 dB时,系统可正常搜索跟踪,扩频环节的接收误码率约达10-5左右,工作状态稳定,有效提高了在变参信道上的传输可靠性。同时经测试,该外围电路也适用于窄带调频方式和其他宽带扩频通信方式。在该领域使用,接收误码率均在允许范围内。

6 结束语

该系统贴近实际电力载波通信特点,力求在满足要求的基础上最简化原理设计,使之实用。每个子系统都参考了相关的方案,精心挑选、可行性论证、改进、设计。其研究成果对于数字信号处理理论及数字通信理论的发展有着一定的意义,同时还可以应用于无线通信、有线通信等领域。

评论