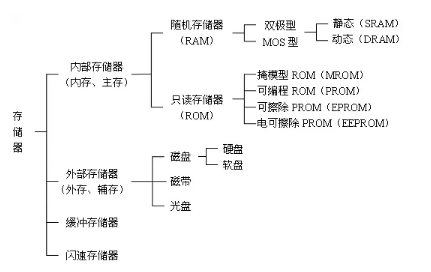

基于SRAM的核心路由器交换矩阵输入端口设计

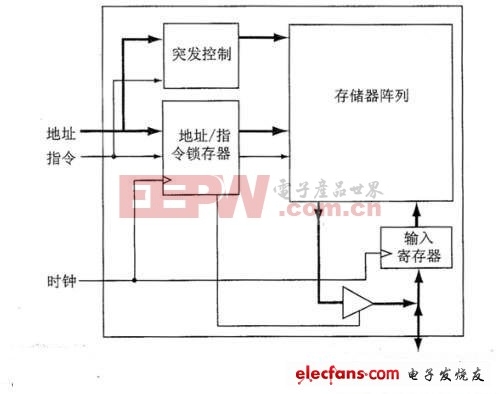

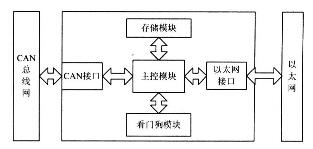

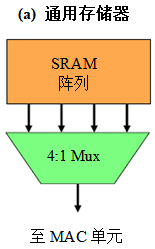

从线卡传输到交换网络输入端口的数据包有着固定的长度,它的长度共有72位,包括6位的包头和66位的包数据。其中包头的前3位是源地址,后3位是目的地址。当报文控制器接收到从线卡传输来的72位的数据包时,便将其存入SRAM中的空地址中,FIFO寄存器是专门用来存放SRAM中的空地址,报文控制器根据FIFO寄存器的空地址将数据包存入到SRAM中,同时更新SRAM地址链接表和VOQ尾指针寄存器,以便接收下一个数据包。当需要从SRAM中读取数据包时,首先根据VOQ头指针寄存器找到SRAM地址链接表,SRAM地址链接表中存放的是数据包在SRAM中的地址,然后根据SRAM地址链接表找到需要从SRAM中读取的数据包的地址,从而读取所需要的数据,同时更新VOQ头指针寄存器和SRAM地址链接表。

由于报文的头尾标志用2 b定义,因此具有很好的故障恢复能力。例如因此硬件传输时受到外界干扰,10标志变成n,这时不需任何例外处理,带来的危害仅仅影响连续的两个报文(两个报文合并成一个)。

4 SRAM读写测试

交换矩阵输入端口的设计取决于能否根据输入端口中FIFO寄存器中的空的SRAM的地址和SRAM地址链接表准确地读取SRAM中的数据报文。该输入端口设计以Atera DE-115开发板上的SRAM芯片为基础,编写SRAM的仿真模型,该芯片的存储容量为2 MB,并在Modelsim中完成了对设计的验证。仿真结果如图4所示。本文引用地址:http://www.eepw.com.cn/article/153526.htm

5 结语

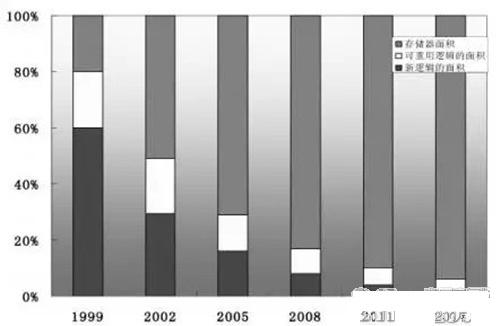

本文设计了一个基于SRAM的交换矩阵的输入端口,该设计有效的消除了输入排队链头阻塞的问题,极大地提高交换开关的利用率,将输入端口数据报文存放在片外SRAM中,可以显著降低交换芯片的面积,提高虚拟队列中数据报文的读取速度,并在Altera开发板上完成了验证,系统性能稳定,具有很好的应用前景与研究意义。

评论