基于ARM与WindowsCE的LCD显示器设计

p_GPIORegs->GPDR1|=(XLLP_GPIO_BIT_L_DD0|XLLP_GPIO_BIT_L_DD1 |XLLP_GPIO_BIT_L_DD2|XLLP_GPIO_BIT_L_DD3

|XLLP_GPIO_BIT_L_DD4|XLLP_GPIO_BIT_L_DD5);

p_GPIORegs->GPDR2|=(XLLP_GPIO_BIT_L_DD6|XLLP_GPIO_BIT_L_DD7

|XLLP_GPIO_BIT_L_DD8|XLLP_GPIO_BIT_L_DD9

|XLLP_GPIO_BIT_L_DD10|XLLP_GPIO_BIT_L_DD11

|XLLP_GPIO_BIT_L_DD12|XLLP_GPIO_BIT_L_DD13

|XLLP_GPIO_BIT_L_DD14|XLLP_GPIO_BIT_L_DD15);

p_GPIORegs->GAFR1_U=(p_GPIORegs->GAFR1_U~(XLLP_GPIO_AF_BIT_L_DD0_MASK|XLLP_GPIO_AF_BIT_L_DD1_MASK|XLLP_GPIO_AF_BIT_L_DD2_MASK|XLLP_GPIO_AF_BIT_L_DD3_MASK|XLLP_GPIO_AF_BIT_L_DD4_MASK|XLLP_GPIO_AF_BIT_L_DD5_MASK))|XLLP_GPIO_AF_BIT_L_DD0|XLLP_GPIO_AF_BIT_L_DD1|XLLP_GPIO_AF_BIT_L_DD2|XLLP_GPIO_AF_BIT_L_DD3|XLLP_GPIO_AF_BIT_L_DD4|XLLP_GPIO_AF_BIT_L_D;

在WindowsCE下都使用虚拟地址,经过一个映射函数将用到的物理地址转化为虚拟地址,这是WindowsCE操作系统所要求的,映射地址的函数为BOOL MapVirtualAddress()。

按照屏的显示模式来配置LCD控制寄存器,其中包括配置LCD控制信号的模式,通过参看IntelPXA270的数据手册和一系列的计算,在掌握TFT LCD时序图的基础上进行参数配置:

L_FCLK为帧时钟;L_LCLK_A0为行时钟;L_BIAS为时钟使能;L_PCLK_WR为像素时钟,LDD17:0>为像素点数据,在本设计中我们只用到了LDD15:0>。

ENB:LCD数据使能位 HSP:水平时钟信号电压极性

0------LCD不可用 0------水平时钟为高电平有效

1------LCD使能 1------水平时钟为低电平有效

PCP:像素时钟电压极性

0------像素数据在数据引脚为上升沿时采样

1------像素数据在数据引脚为下降沿时采样

(1)行列的定义:

PPL: LCD屏的水平像素点的个数。根据LCD屏的长度来确定其值的大小。

PPL =行宽-1

在本设计中,行宽为800,那么PPL=800-1;

LPP: LCD屏的垂直像素点的个数。根据LCD屏的宽度来确定其值的大小。

LPP=列高―1

在本设计中,列高为480,那么LPP=480―1;

(2)L_PCLK_WR:

VCLK是LCD控制器的时钟信号,此信号是LCD控制器和LCD驱动器之间的象素时钟信号,VCLK计算时需先了解LCD屏所要求的帧速率的范围,并由此设定一个在帧速率范围内的值为CLKVAL,VCLK与CLKVAL之间的关系可用如下公式计算:VCLK(Hz)=HCLK/((CLKVAL +1)x2)

最小的CLKVAL为0,最大的CLKVAL由帧速率决定[8]。

(3)各种延时的取值:

BFW:一帧开始时所需要的延时长度

EFW:一帧结束时所需要的延时长度

VSW:帧同步信号VSYNC的宽度定义

BLW:一行开始时所需要的延时长度

ELW:一行结束时所需要的延时长度

HSW:行同步信号HSYNC的宽度定义

4 结束语

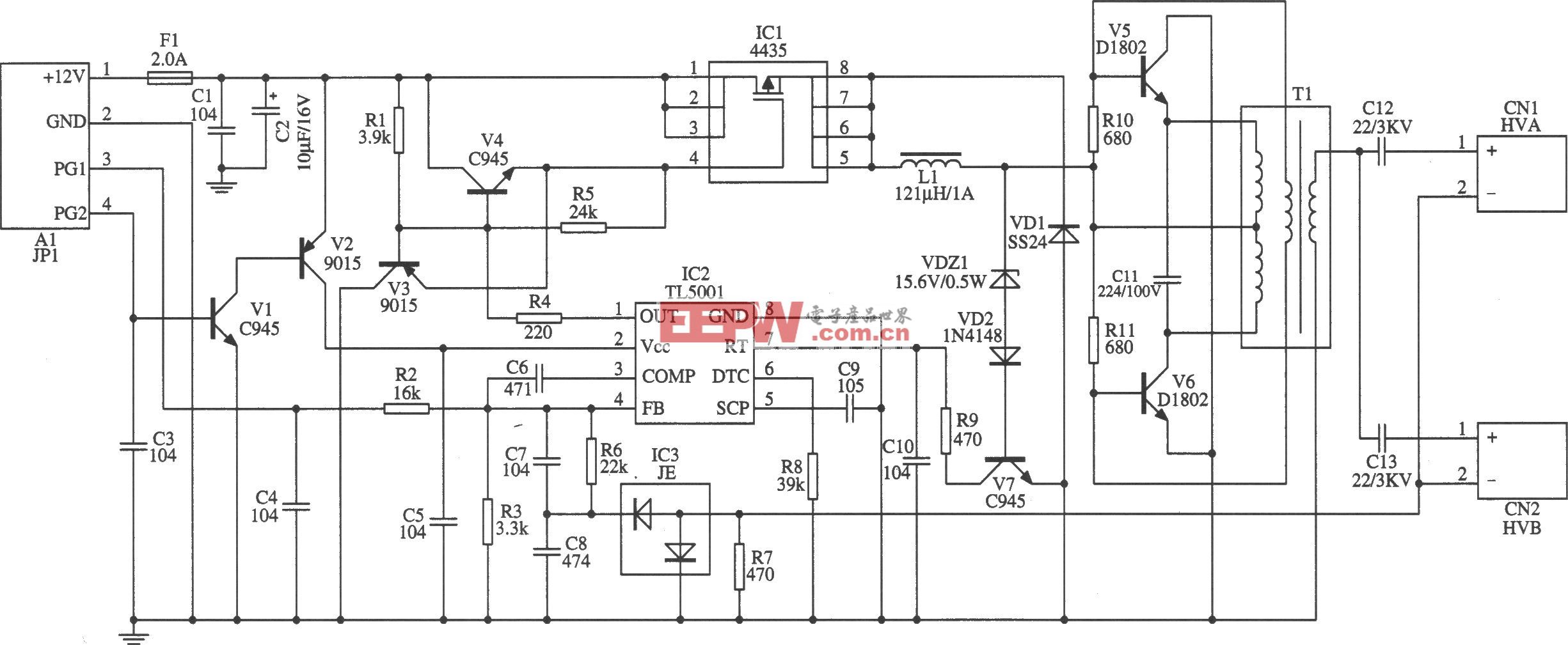

基于嵌入式处理器IntelPXA270和WindowsCE进行LCD显示器设计,采用LCD驱动TFT显示屏,显示模式是主动的单扫描彩色模式,像素深度为16位的RGB格式,屏的大小为800×480。通过充分利用IntelPXA270的硬件资源,用IntelPXA270 控制彩色显示屏,显示亮度达100尼特,在LCD 高亮度的情况下显示器的功耗小于365 mW ,克服了一般TFT LCD 高亮度伴随着高功耗的矛盾;支持用户定制的TFT 液晶屏上实现WindowsCE 界面的图形显示;由于设计的硬件驱动电路只需LCD控制器给出帧同步信号、行同步信号、像素时钟、数据使能信号和RGB数据信号,因此,设计的驱动电路能灵活地移植到不同平台。

评论