基于ARM和FPGA的嵌入式高速图像采集存储系统

2.2 FPGA模块

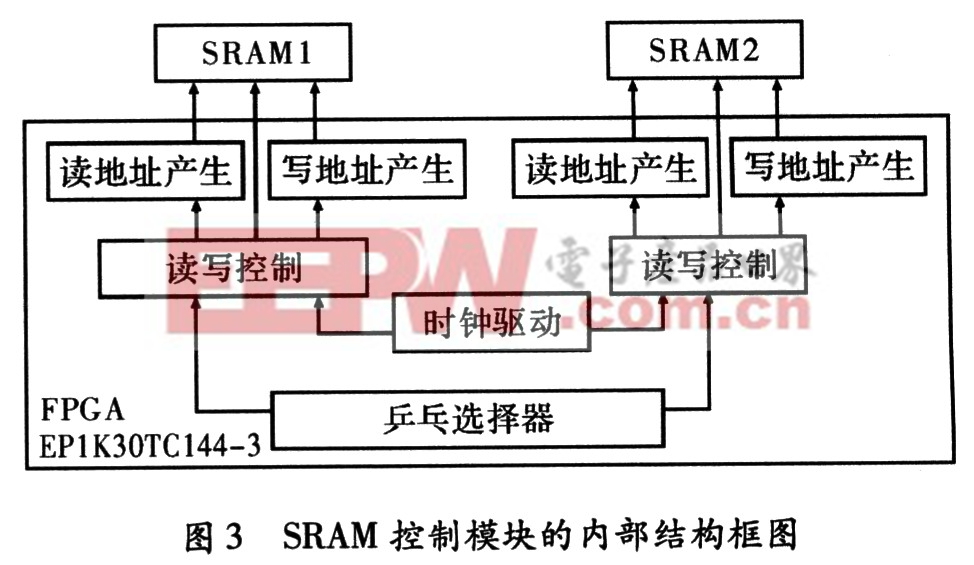

FPGA主要作用是把图像采集芯片传过来的图像原始数据,采取乒乓操作的方式,暂存于两片SRAM中。当FPGA开始接收第一帧图像时,把该帧图像根据FPGA内部生成的地址存储在SRAMl中,一帧图像接收完毕后,向ARM传送。同时,把下一帧图像暂存于SRAM2中,然后传给ARM,依次循环。这样就可以实现图像的高速采集。本系统选用了Alter公司的EPlK30TCl44―3,它采用EECMOS技术,144引脚TQFP封装,容量为10万门,具有高密度、低成本、低功耗的特点。FPGA的内部结构包括时钟驱动模块、SAA7113H控制模块、SRAM控制模块、ARM数据交换模块等。SAA7113H控制模块主要负责对视频采集芯片SAA7113H的初始化和启停等功能控制;SRAM控制模块则主要进行读写地址生成、“乒乓”读写控制等;ARM数据交换模块负责向ARM申请中断和数据传输。这些模块在设计中利用VHDL语言,在Quartus II环境下进行编程和调试,具体实现方法参见文献。本系统中,主要针对640×480的灰度图像的采集和存储,所以选用了ISSI公司的IS6lIN25616AL,它是一种高速度、低功耗的256 kB×16的CMOS静态随即存储器,能够满足系统的实际要求。SRAM控制模块的内部结构框图,如图3所示。本文引用地址:http://www.eepw.com.cn/article/152552.htm

2.3 ARM模块

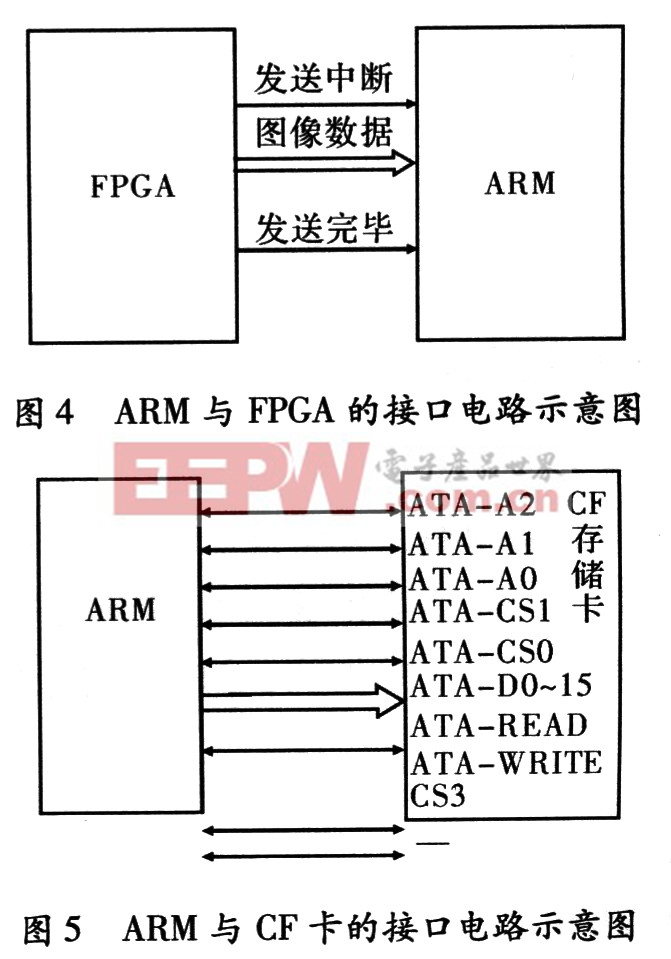

ARM模块的主要作用是,从SRAM中取出图像原始数据,然后进行必要的处理,再存储在大容量的CF卡上,方便用户在PC机上对图像进行必要的处理操作。FPGA接收完一帧图像后,向ARM发出中断请求,ARM收到请求后,通过FP―GA将SRAM中的数据读入。一帧数据发送完毕后,FPGA发出发送完毕信号,ARM对接收到的数据进行必要的处理后,将数据存储在大容量的CF卡上。本系统选用了Philips公司的LPC2214,它是基于ARM7TDSI体系的嵌入式微处理器,内部具有16 kB的静态随机存储器和256 kB的Flash程序存储器,可实现高达60 MHz的工作频率。ARM与FPGA及CF卡的接口电路分别,如图4,图5所示。

评论