基于FPGA/CPLD的嵌入式VGA显示系统

VGA时序发生器模块产生显示器所需的时序,这是完成设计的关键,时序稍有偏差,显示必然不正常,甚至会损坏彩色显示器。 3、 VGA时序分析

显示器采用光栅扫描方式,即轰击荧光屏的电子束在 CRT(阴极射线管)屏幕上从左到右(受水平同步信号 HSYNC控制)、从上到下(受垂直同步信号 VSYNC控制)做有规律的移动。光栅扫描又分逐行扫描和隔行扫描。隔行扫描指电子束在扫描时每隔一行扫一线,完成一屏后再返回来扫描剩下的线,与电视机的原理一样。隔行扫描的显示器扫描闪烁的比较厉害,会让使用者的眼睛疲劳。目前微机所用显示器几乎都是逐行扫描。逐行扫描是指扫描从屏幕左上角一点开始,从左向右逐点进行扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;当扫描完所有行,形成一帧时,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行行场消隐,开始下一帧的扫描。

完成一行扫描所需时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描所需的时间称为垂直扫描时间,其倒数为垂直扫描频率,又称刷新频率,即刷新一屏的频率。常见的有 60Hz、75Hz等。

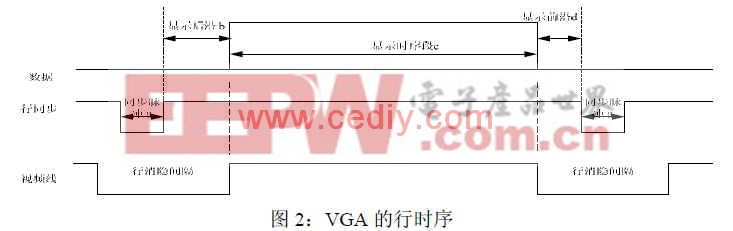

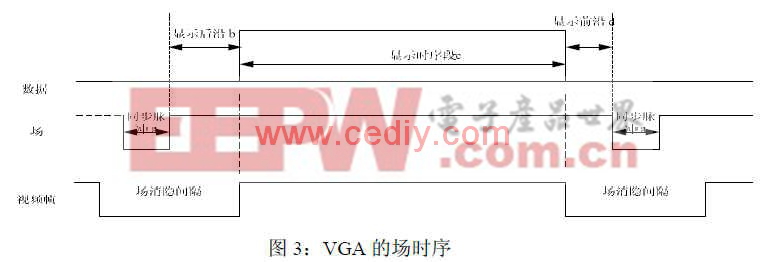

VGA显示器要正确显示图像关键还是如何实现 VGA时序。视频电子标准协会( VESA, Video Electronics Standards Association)对显示器时序进行了规范。 VGA的标准参考显示时序如图 2、图 3所示。行时序和场时序都需要产生同步脉冲(Sync a)、显示后沿 (Back porch b)、显示时序段(Display interval c)和显示前沿 (Front porch d)四个部分。 VGA工业标准显示模式要求:行同步、场同步都为负极性,即同步头脉冲要求是负脉冲。

VGA的行时序如图 2所示:每一行都有一个负极性行同步脉冲( Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿 (Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个象素点,从而显示一行。在一行的最后为显示后沿(Back porch b)。在显示时序段( Display interval c)之外没有图像投射到屏幕时插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内( Horizontal Blanking Interval),当行消隐有效时, RGB 信号无效,屏幕不显示数据。

本文引用地址:http://www.eepw.com.cn/article/152392.htm

VGA的场时序与 VGA的行时序基本一样,如图 3所示,每一帧的负极性帧同步脉冲(Sync a)是一帧的结束标志,同时也是下一帧的开始标志。而显示数据是一帧的所有行数据。

评论