多对一嵌入式税务控制器研究初探

4.3 使用双处理器嵌入式税务控制器实现“多对一”:

该方法不需在软件设计上增加并行计算,原有的税控软件可直接移植到嵌入式税务控制器中即可使用。该嵌入式税务控制器采用双处理器,共享内存,其它如嵌入式的IO、网卡、税控芯片及闪存 flash的连接与单处理器相同。此时控制器的算法依然采用多线程技术,只是由于现在增加了处理器的数量,线程的调度、运行效率将大大提高。

5 多对一嵌入式税务控制器的硬件设计实现:

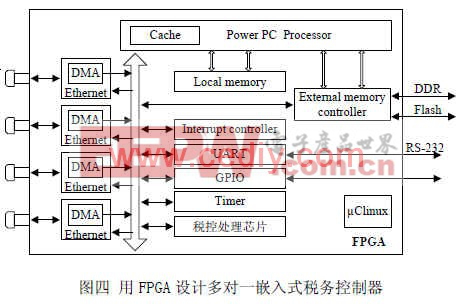

我们采用 FPGA技术进行多对一嵌入式税务控制器设计。

FPGA(Field Programmable Gate Array,即现场可编程门阵列),可提供高性能的数据和控制处理功能,具有规模大、可重复编程、开发投资小等优点,在现代电子产品中应用得越来越广。因此,利用 FPGA技术实现多对一嵌入式税务控制器是较好的设计方案。

在本文,使用Xilinx 的 VirtexO-4 FX进行设计,VirtexO-4 FX内建 PowerPC双处理器,能对数据进行高速并行处理,效能提升很大。VirtexO-4 FX FPGA包含高性能的可编程架构、嵌入式 PowerPC处理器和 3.125Gbps收发器,从而成为嵌入式税务控制器的理想选择。实现方案如图四所示。

本文引用地址:http://www.eepw.com.cn/article/152383.htm

6 结束语

采用多对一嵌入式税务控制器是降低商家税控系统采购成本,进而顺利推进商业税控自动化的非常重要的技术环节。在本文,分析了无线、有线两种连接嵌入式税务控制器的组成形式,提出了用并行架构及双处理器来实现多对一嵌入式税务控制器的设计思想,提出了多对一嵌入式税务控制器硬件实现的基本方法,即 FPGA方法。用并行架构和采用集线嵌入式税务控制器及多线程技术实现多对一是本文的创新点,它为更好地提高现有嵌入式税务控制器的处理效率、减少商场采购压力、和在现有条件下实现更先进的税务控制等方面提供了更深层次的设计思路和解决办法。

pos机相关文章:pos机原理

评论