基于FPGA和DDS的信号源设计

4 DDS的FPGA实现

4.1 相位累加器与相位寄存器的设计

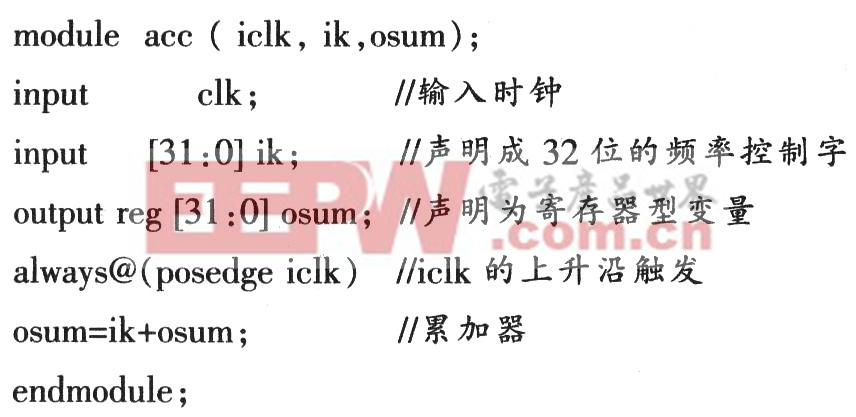

相位累加器与相位寄存器主要完成累加,实现输出波形频率可调功能。利用Quartus II可编程逻辑器件系统开发工具进行设计。首先,打开Quartus II软件,新建一个工程管理文件,然后在此工程管理文件中新建一个Verilog HDL源程序文件,并用硬件描述语言Verilog HDL编写程序实现其功能。在设计过程中,可在一个模块中描述。一个参考的Verilog HDL程序如下:本文引用地址:http://www.eepw.com.cn/article/152260.htm

4.2 基于1/4波形的存储器设计

为了提高系统的分辨率和降低FPGA资源的利用率,采用基于1/4波形的存储器设计技术。利用正弦波对称性特点,只要存储[O~π/2]幅值,通过地址和幅值数据变换,即可得到整个周期内的正弦波,其设计原理如图2所示。

用相位累加器输出高2位,作为波形区间标志位。当最高位与次高位都为“0”时,表示输出正弦波正处在[0~π/2]区间内,这时,地址与输出数据都不需要变换;当最高位为“0”,次高位为“l”时,输出正弦波正处在[π/2~π]区间内,这时,地址变换器对地址进行求补操作,而输出数据不变;当最高位为“l”,次高位为“0”时,输出正弦波正处在[π~3π/2]区间内,这时,地址不变,而输出变换器对输出数据进行求补操作;当最高位与次高位都为“l”时,输出正弦波正处在[3π/2~2π]区间内,这时,地址和输出数据都进行求补操作。

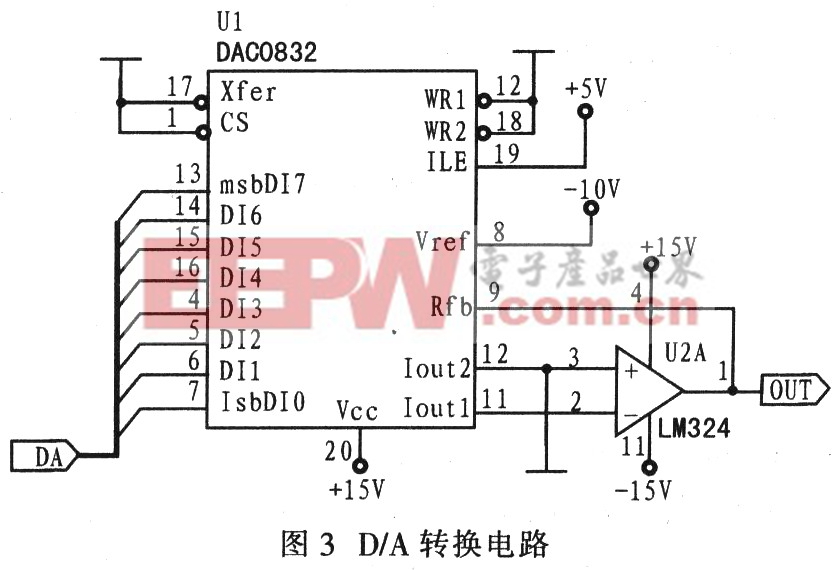

5 D/A转换电路

数据转换器输出的数据是数字形式的电压值,为实现数字电压值与模拟电压值之间的转换,系统还专门设计D/A转换电路,其D/A转换电路原理图如图3所示。

为降低设计成本,采用8位廉价DAC0832作为转换器。该器件是倒T型电阻网络型D/A转换器,因其内部无运算放大器,输出为电流,所以要外接运算放大器,本文采用LM324型运算放大器。DAC0832可根据实际情况接成双缓冲、单缓冲和直冲3种形式,这里采用第3种连接形式,即引脚1、引脚2、引脚17、引脚18接低电平,引脚19接+5 V。引脚8为参考电压输入端口.接至+1O V的电源,当数字输入端全为高电平时,模拟输出端为+10 V。

评论