FPGA的时钟频率同步设计

本文引用地址:http://www.eepw.com.cn/article/152175.htm

4 实验验证

主时钟采用50 MHz的有源晶振来实现,并将其作为固定时钟;从时钟采用30 MHz有源晶振,通过FPGA的锁相环PLL将其频率倍频到60 MHz,然后1.2分频,实现可调频率的50 MHz时钟。

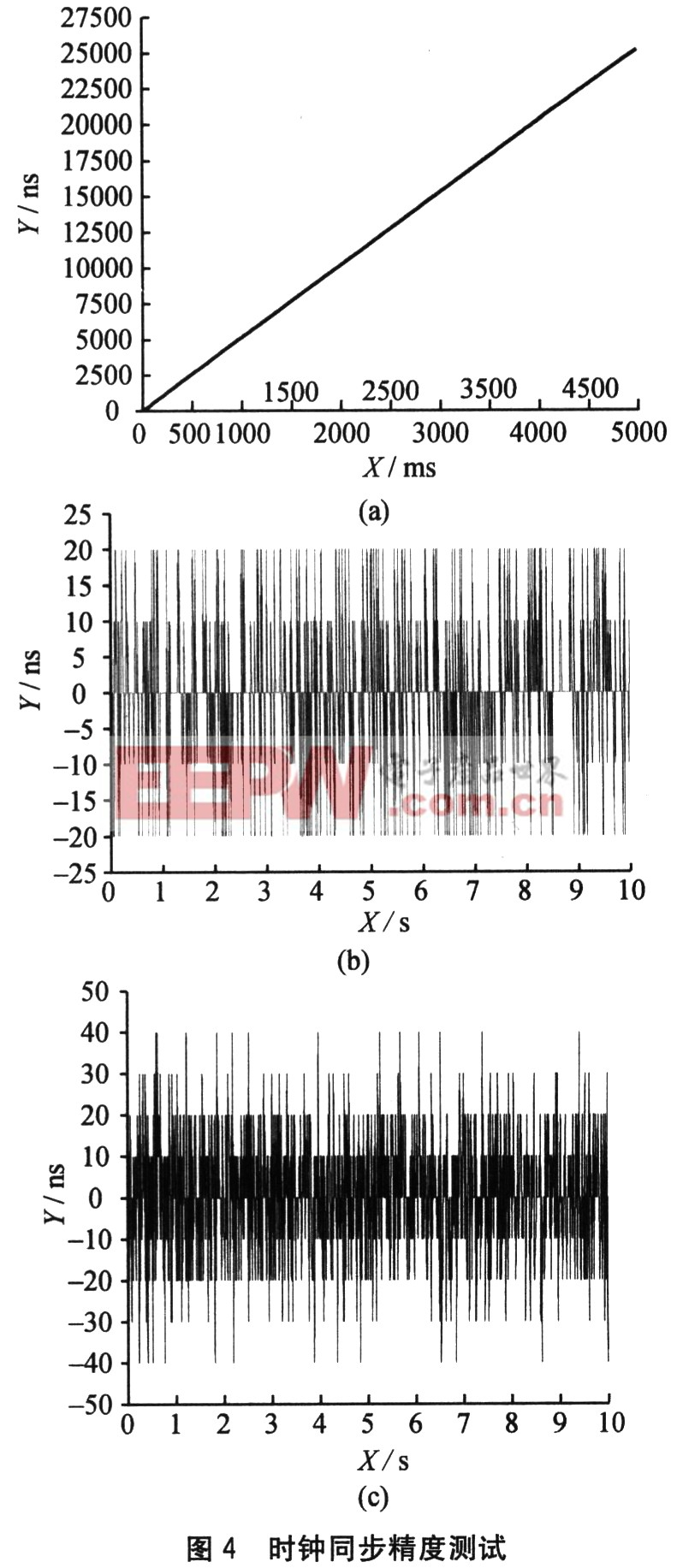

让主时钟和从时钟以一定的时间间隔产生中断,并通过逻辑分析仪采样中断信号分析其偏差。由于系统时钟的分辨率为20 ns,采用广州致远电子有限公司的逻辑分析仪LA1532,其最大采样频率为100 MHz,所以偏差测量精度可以达到10 ns。图4(a)是未进行同步前两个时钟的偏差分析,X轴表示主时钟和从时钟的计时长度,Y轴表示主时钟和从时钟的计时偏差。从图中可以看出两个时钟的偏差大概为5×10-6,即1 s内的偏差可以达到5μs。图4(b)为同步后主时钟和从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±20 ns。X轴表示测量时间,Y轴表示主从时钟同步偏差。图4(c)为同步后两个从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±40 ns。X轴表示测量时间,Y轴表示从时钟之间同步偏差。

结 语

基于时钟频率调整的时间同步方法,实现简单,而且没有复杂的软件同步协议,占用较小的网络带宽就可以实现高精度的时钟同步,在硬件上只需要低成本的FPGA支持。

伺服电机相关文章:伺服电机工作原理

评论