FPGA的时钟频率同步设计

3 频率补偿算法在FPGA中的实现

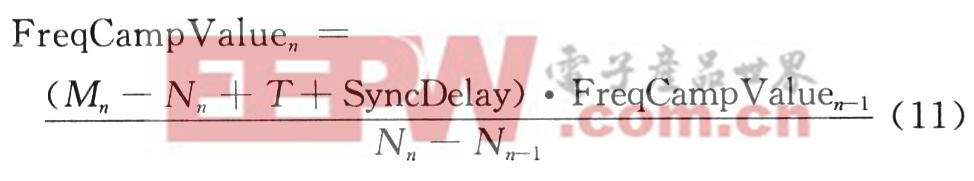

由式(4)和式(10)可得:

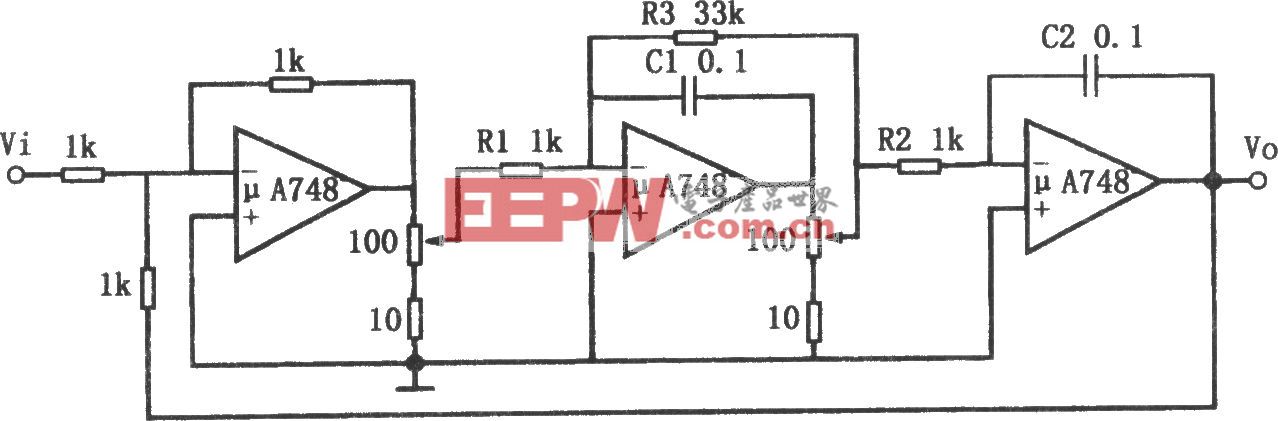

频率补偿就是在每个同步周期计算FreqCompValuen,FPGA提供了参数化的乘法器兆函数(1pm_mult)和除法器兆函数(1pm_divide),可以快速实现上述算法。原理如图3所示,在每个同步周期同步信号的驱使下,锁存器B和C分别锁存当前时钟读数和上个同步周期时钟读数,同时将主时钟读数输入到加法器A中,经过减法器E、F和乘法器G,以及除法器H后计算出新的FreqCompValuen,并在同步信号的驱动下,将其锁存到锁存器D中。由于中间的计算结果要经过一定的时钟周期,所以锁存器D的锁存信号要延时一定的晶振周期。在本设计中延时50个FreqOsc,即在1μs的情况下就可以得到新的频率补偿值。本文引用地址:http://www.eepw.com.cn/article/152175.htm

同步报文的传输延迟SyncDelay理论上是不变的,而实际上报文在传输过程中有抖动。参考文献[3]对此进行了分析,并指出同步周期越长,报文传输延迟抖动的影响就越小,因此可以忽略不计。

伺服电机相关文章:伺服电机工作原理

评论