通过分布式处理提升处理器效率

在刚刚过去的数年内,我们见证了多处理系统日渐成为主流,事实上大多数现代个人计算的CPU均采用了对称多处理系统(SMP),其中,相同处理器的多个实现例程分担运行在PC上的应用程序负荷。SMP目前已相当常见,但在嵌入式计算中,向多处理的转移趋势并不常见。然而,新的嵌入式设计技术为工程师提供了相当的自由度,能够在数字子系统上智能化地分配处理功能。在本文中,研究了一个使用Cypress半导体公司PSoC 3和PSoC 5架构的分布式处理技术示例,该架构由一个主CPU(在本例中为8051或ARM Cortex M3)、一个DMA引擎、以及通用数字模块(UDB)阵列构成。UDB可高效用作微处理器阵列。通过在这类子系统上分配处理功能,减少计算复杂程度和处理负荷,工程师能够提升整个系统的效率。

本文引用地址:http://www.eepw.com.cn/article/152160.htm将处理功能分解到多个功能块上具有很多优点,最大的优点是降低了实际功耗。通过降低CPU在处理MIPS方面的负荷,只计算简单的函数,如服务中断,能够以较低的频率运行应用程序,这是因为,除了应用程序的所有函数外,CPU无需在不太复杂的函数上耗费指令周期。这样,就能从两个方面降低整个应用的功耗。第一个优点显而易见,降低CPU时钟,随着时钟速度的降低,实际功率呈线性下降。第二个优点有些容易被忽视,但同样重要,CPU具有的逻辑门约是UDB的10倍以上,通过将处理功能从主CPU卸载到微处理器上,可释放大量用于完成处理功能的逻辑门,从而进一步显著改善实际功耗。

除了显著降低应用程序的实际功耗外,分布式处理还具有另一项优点,由于CPU从更平凡的处理负担中解脱出来,能够将其MIPS更多地用在可更好发挥CPU特性的功能上,用于具有更高计算强度的函数上,如乘除指令。

为了理解将处理功能分解在架构上的方式,我们将分析常见的嵌入式应用,如无刷直流电机控制。首先我们深入实质,了解PSoC 3和PSoC 5数字子系统,以便理解其能力。

PSoC 3和PSoC 5器件公用平台架构,这意味着在两个系列中,基本硬件是相同的。PSoC3和5平台架构由四个主要功能块构成,它们是:

CPU子系统:首先是CPU子系统,它包含主CPU(8051或Cortex M3)以及所有支撑IP,包括中断控制器,调试硬件,以及DMA控制器。其他系统功能也包含在CPU子系统中,如计时,电源管理,以及系统存储器。通过CPU与DMA引擎的结合,可为我们提供实现分布式处理功能所需的两个关键部件。

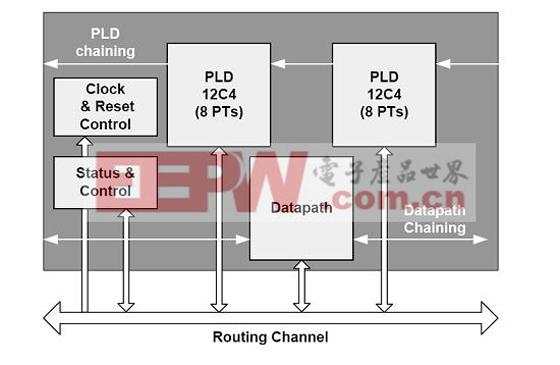

数字子系统:数字子系统是PSoC 3和PSoC 5系列架构的另一重要部分,使用它,能够实现分布式处理系统。PSoC 3和PSoC 5中的数字子系统主要由可灵活编程的通用数字模块(UDB)阵列构成。正如从图X中所见到的,UDB硬件包含数据路径元素,它本质上是8位微处理器,能够执行标准的处理功能,如移位、加和比较。数据路径元素(图XX)还与PLD单元相结合,可用于实现定制的逻辑功能,甚至能够查询表以找出可用作参考的数据路径元素。这些UDB可用于实现很多外围标准功能,如PWM、定时器和SPI,它们也能用于实现定制的外围功能。正因为这种灵活性,PSoC能够实现分布式处理功能。

图1

评论