基于模型的DDS芯片设计与实现

2 在MATLAB 中建立的DDS 模型并在ISE 中实现本文引用地址:http://www.eepw.com.cn/article/152145.htm

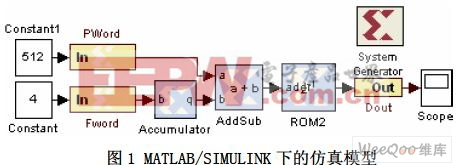

Simulink 是一个可用于多领域动态系统仿真的平台,为动态系统提供建模和分析的方 法,提供交互的图形化方框图环境带有为信号处理、通信和控制等可定制的模块集。System Generator 就是Xilinx 公司的一个专有模块集(Blockset),它是Simulink 的一个插件, 包括基本DSP 函数和逻辑算符,其中包含的预先定义好的模块可以保证FPGA 实现时位和周 期的正确。用它可以自动生成VHDL 语言、测试向量等文件,还可以自动将特定的设计模块 映射成高度优化的IP 核模型。在本文介绍的设计中,最后生成的工程文件中就自动映射出 一个累加器核和一个单口块ROM 核。

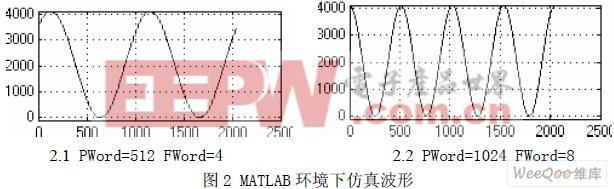

根据DDS 控制原理在MATLAB 环境中建立如下的模型(图1):其中在存储正弦数据的RO中设定Depth 为:4096,Initial Value Vector 为:2047*sin(pi*(0:4095)/2048)+2047, 即让System Generator 在编译过程中自动产生一个存储4096 个正弦数据的ROM。为了配合 使用开发板上的D/A 模块,ROM 中的每个值设置成12 位无符号数。Accumulator 模块用来进 行相位的累加,AddSub 模块将相位偏移量与相位累加值相加,作为ROM2 的地址输入。在仿 真前,设置相位控制字为PWord=512,由公式算出移相后的波形应该较基准正弦波偏移 ;设置频率控制字FWord=4,将仿真时间设置为2048,这样 从理论上我们应该可以看到两个周期的完整波形输出。运行仿真,可以在Scope 中观察到如图2.1 中波形。改变控制字的值,就可以得到不同频率、不同相位的波形(图2.2)。

;设置频率控制字FWord=4,将仿真时间设置为2048,这样 从理论上我们应该可以看到两个周期的完整波形输出。运行仿真,可以在Scope 中观察到如图2.1 中波形。改变控制字的值,就可以得到不同频率、不同相位的波形(图2.2)。

2.2 在ISE 中实现并仿真

点击System Generator 图标中的generate 按钮,生成可综合的VHDL 代码,并在ISE 中打开。先对代码使用Synthesize-XST 进行综合,通过之后可以观察到系统RTL 级视图。 然后创建一个.tbw 文件对综合后的设计进行仿真,能够得到和MATLAB 环境下一样的仿真结 果(按照正弦规律变化的离散数值序列)。为了能够在实验板上实现设计,在ISE 环境中建立 顶层文件,将System Generator 产生的文件与PicoBlaze 的控制程序文件结合,再进行对 应的功能仿真,正确后加载约束文件,生成比特流文件。

隔离器相关文章:隔离器原理

评论