基于PC104总线的2FSK调制器的设计与实现

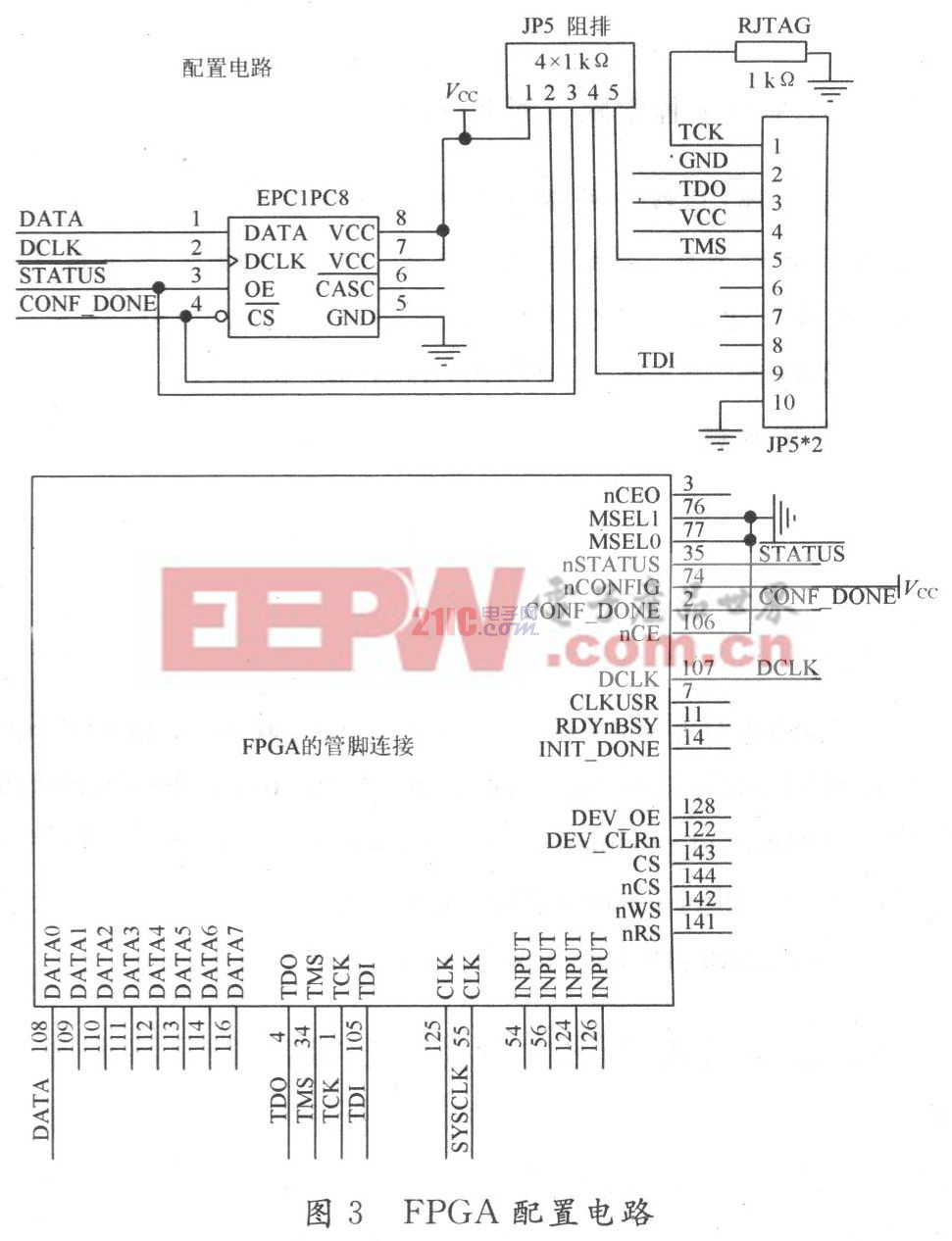

FPGA配置电路如图3所示。本文引用地址:http://www.eepw.com.cn/article/152019.htm

FPGA的配置使用PS和JTAG两种方式,既能实现JTAG方式下电路在线调试,又能保证调试完成后能够正确使用相应的配置器件。其中JP5*2插座为JTAG配置端口,TDI、TDO、TMS、TCK为JTAG配置引脚,该配置方式采用BlasterMV线,通过配置计算机的并口与电路板配置端口进行连接,用于将编写好的配置数据实时传送到FPGA,该方式主要用于电路调试;EPC1C8为FPGA配置器件,采用PS(被动串行)配置方式,由于FPGA内部存储器属于易失性RAM存储因此每次加电后都要将程序重新写入FPGA,配置器件本身就是存储器,其主要作用就是在每次加电后将程序写入FPGA,保证调试完毕的电路能够正常单独进行工作。

来自前级电路的数据及控制信号、发到D/A转换电路的数据都连接到FPGA芯片的通用I/O引脚,通过编程实现所需功能。对FPGA的编程使用Altera公司的QuartusⅡ软件,该软件采用图形化与VHDL语言混合编程,易于调试修改。编程实现的主要功能为:对输入数据进行锁存移位,确保每位数据都能得到正确处理;产生两组分频时钟参与2FSK调制,并使分频后的时钟按照时序进入数字调制器;数字调制器负责将不同频率始终按照顺序依次产生连续量化的8位正弦波数字量输出到端口。

本设计中由于采用两种频率分时产生,按时序进入调制器,而正弦波数字调制器单独工作的方法,保证了输出正弦波具有连续的相位,不会产生相位突变。

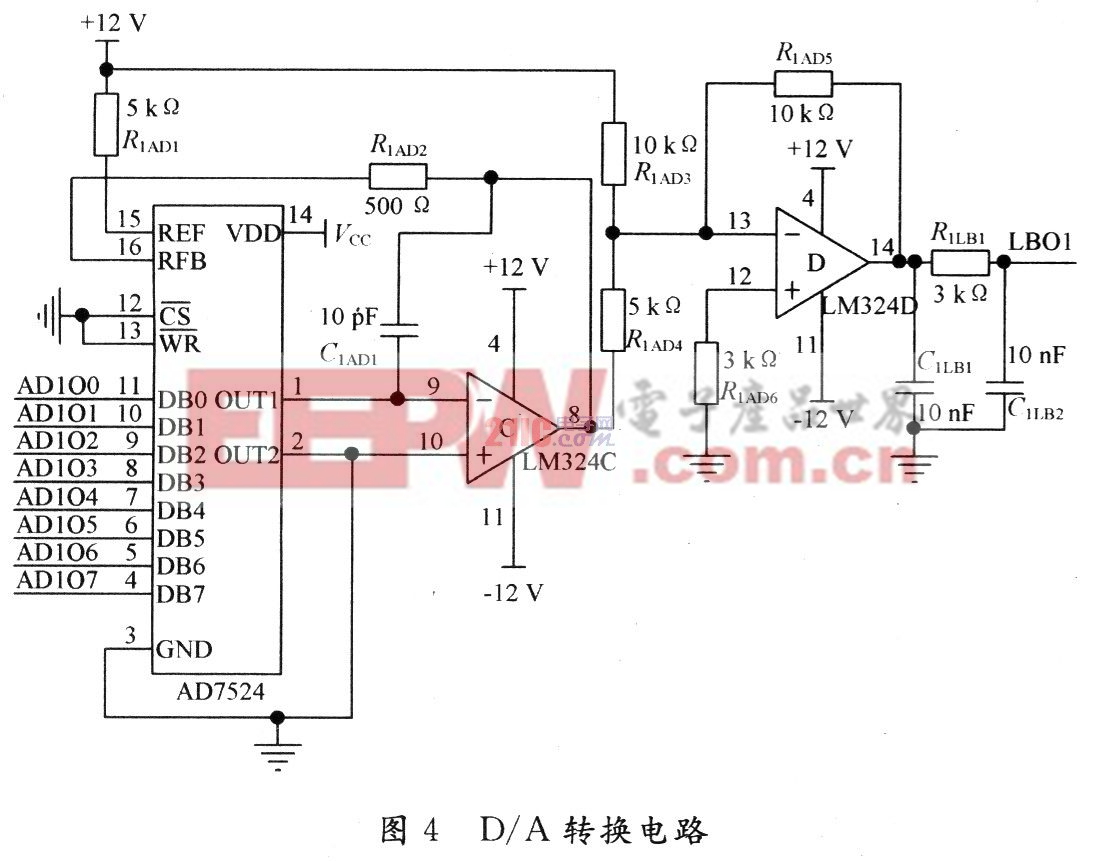

4 D/A转换电路

D/A转换共包括四路,其主要功能是将FPGA输出的已调制好的2FSK数字信号转换为正弦波信号。由于FPGA在进行数字调制时产生的是连续量化的正弦波形,两个频率之间不存在相位的突变,不会存在大量的高频杂波,因此,后期的信号处理电路使用放大电路与简单的丌型滤波器对信号进行处理即可得到比较理想的2FSK信号。

D/A转换电路如图4所示。

此电路采用AD7524作为D/A转换器,AD7524属于T型电阻网络型DAC,电流输出,8位数字输入,输出建立时间O.2 μs/0.15μs,其数字输入端可采用5 V/15 V两种输入,本电路采用兼容TTL电平的5 V输入。电路中将其输入控制端CS、WR同时接地,当有来自FPGA的数据AD1O1~7输入时无需锁存,直接进行转换,因此要求FPGA的输出要具有锁存功能,此接法可减少输出控制线,减少时序干扰。R1AD1和R1AD2为D/A输出波形调整电阻,主要用于调整波形位置,不致产生失真。D/A输出采用双极性接法,通过两路LM324通用放大器进行电压放大,输出2FSK信号。图5(a)为经过D/A转换后输出的波形在示波器上的截图,由图中可以看到,数字调制并经D/A转换后,波形是一种阶梯状正弦波,且波形连续,频率变换交界处无相位突变。该信号经过双极性放大器放大并通过丌型滤波器后变成如图5(b)所示的连续正弦波。

评论