基于S3C2510A的嵌入式数字硬盘录像机的设计

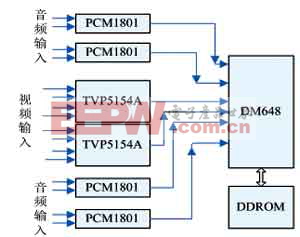

图4中,TVP5154A的CH1_OUT,CH2_OUT,CH3_OUT,CH4_OUT口与1片DM648的VP0,VP1口直接连接,组成1个8路的视频采集,压缩模块,用于数据的传输。DM648通过I2C总线对TVP5154A内部寄存器进行读写,达到控制该芯片的目的。

图4 视音频采集压缩模块框图

音频输入采集模块由8个PCMl801U型音频采集电路及其外围电路组成,主要功能是对由拾音器采集输入的模拟音频信号进行采样,然后将其转换为DSP可以处理的数字音频数据格式。PCMl801U是采用5V工作电压的双声道16位音频模/数(A/D)转换器,包括1个单端-差分模拟前端、1个5阶△一∑调制器(64倍重复取样)、1个内部高通数字均分滤波器。

DM648有专门的McASP,与4个PCMl801U连接,实现音频的输入采集功能。用PCMl801U的左、右2个16位音频声道获取4路音频通道的数字化数据,音频采集的数据格式为每路单声道、44.1kHz采样率,每个采样数据用8位量化。采集输出的数字音频数据通过McASP传给DSP的输入缓冲区单元,当设定用于存放音频采样数据的缓存器已满时产生DMA中断,并在DMA中断服务程序中根据实际设定情况处理音频数据,经过实时编码压缩后的音频数据存储到外部SDRAM中。

PCB设计

本系统的主频高达166MHz,属于高频系统,所以在进行PCB的设计时,必须进行抗高频干扰的设计与处理。DM648作为高性能数字媒体处理器不仅内部具有很高的运行频率,而且与外部的DDRAM的总线速度也达到266MHz或333MHz,如果外部的DDRAM由于布线原因达不到设计的希望速度,会降低系统的性能。此外由于100MHz以上的信号总线,存在信号完整性问题。为了保证信号的完整,在设计的时候采用了如下方法:

(1)对DDRAM的时钟线,尽量走短线,而且到两个DDRAM的长度尽量做到相等;

(2)FLASH等其他外设不要直接与数据和地址总线连接,而是通过缓冲芯片(如SN74LVT16245B)连接;

(3)高速总线上串入了小阻值电阻,阻值大小通过Protel软件仿真得到,同时对线路进行了阻抗限制。

此外,由于DM648内部有PLL,对PLL外部所接器件,让它们尽可能的靠近芯片,而且只放在了线路板的一面上。对于JTAG的连线长度不超过6英寸,如果超过6英寸长的加了驱动。本系统中既有模拟部分又有数字部分,所以在设计的时候,特别注意了模拟电源和数字电源的设计,尽量减少数字信号对模拟信号的干扰,否则对采集的视频信号会有雪花、条纹,音频信号产生噪声等。对视频、音频芯片采用了单独的电源芯片供电,模拟地和数字地通过单点或采用磁珠相连。

以上的抗高频干扰方法的采用,使得整个系统在调试的过程中能够顺利的进行。

评论