基于NioslI的SOPC系统的LCD显示驱动IP核设计

引言

本文引用地址:http://www.eepw.com.cn/article/151605.htmNioslI嵌入式处理器是A1tera公司提出的SOPC解决方案,是一种用户可随意配置和构建的32位嵌入式处理器,结合丰富的外设可快速、灵活地构建功能强大的SOPC系统。Altera公司提供了一些通用的IP核,使得用户可轻松集成属于自己的专用功能;但对于一些特定的外设,没有现成可用的IP核,如液晶模块CBGl28064等。

本文以深圳秋田视佳实业有限公司的液晶显示模块CBGl28064为例,在基于NioslI的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

1 CBGl28064液晶显示模块

CBG128064是一款以2片HD61202作为列驱动器,1片HD61203作为行驱动器的液晶模块。HD61202是一种带有驱动输出的图形液晶显示控制器,可直接与8位微处理器相连;而HD61203只需提供电源,就能产生行驱动信号和各种同步信号。CBGl28064液晶显示模块内置显示存储器RAM,显示屏上各像素点的显示状态与显示存储器RAM中的各位数据一一对应。显示存储器的数据直接作为图形显示的驱动信号。外部处理器只需要通过其8位数据线和6条控制线来设置所需要的显示方式,其他功能均由模块自动完成。HD61202提供7条简单的指令:显示开/关指令、显示起始行(ROW)设置指令、页(RAGE)设置指令、列地址(Y Address)设置指令、读状态指令、写数据指令、读数据指令。

2 方案选择

通常有两种方式可以实现NiosII嵌入式处理器对LCD的显示驱动:

一种是利用现成的并行输入/输出(PIO)内核。该内核提供了Avalon总线从控制器端口到通用I/O口间的存储器映射接口,将LCD模块的接口与NiosII嵌入式处理器的并行端口相连接,NiosII嵌入式处理器通过对其端口的操作来完成对LCD模块的控制。这种方式类似于单片机操作,时序简单,易于实现;但是在SOPC系统中硬件上需要设计与外设相连的I/O口,软件上需要编写接口程序进行读写控制,增加了处理器的时间开销,FPGA的并行处理能力没有得到发挥。

另一种是采用自定义IP核方式。把LCD模块看成是外部存储器或I/O设备,作为从设备挂接到NiosII嵌入式处理器的Avalon总线上,处理器以访问I/O设备或读写存储器的方式对其进行控制。这种方法需要写HDL模块,自己定义控制、状态、数据寄存器和控制位,可较为灵活地实现复杂的时序控制。一旦完成了设计,即可封装为SOPC BLdldel可用的独立元件,用户可以像使用Altera公司提供的其他外设一样来使用,并且可以提供给其他设计者使用。本文选用该方式实现。

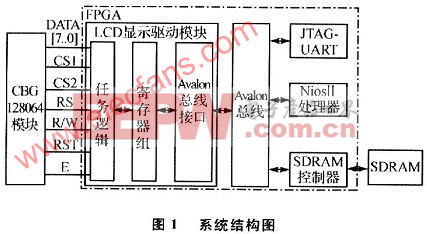

3 LCD显示驱动设计

图l为系统结构图。设计的重点在于LCD显示驱动模块的设计。按照模块化、层次化的设计思想,显示驱动可分为3部分实现,即任务逻辑部分、寄存器组部分和Avalon总线接口部分。任务逻辑部分描述液晶模块的读写逻辑功能;寄存器文件部分提供了内部寄存器访问的通道;Avalon总线接口部分通过顶层接口模块对寄存器进行操作,从而实现对行为模块的访问和控制。其中,DATA[7..0]为8位数据线,CSl、CS2为片选信号,RS为指令/数据选择信号,R/W为读写选择信号,RST为复位信号,E为读写使能信号。

评论