高速并行RS解码器

3.3 改进的流水线结构

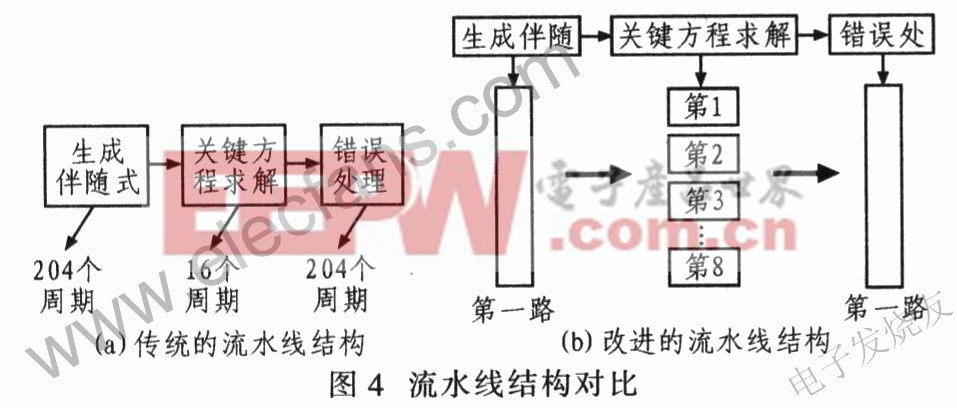

图4给出了传统和改进的流水线结构对比。传统的流水线结构各模块处理周期差距很大,约达8:1比例,造成周期极大浪费。改进的流水线结构则采用时分复用,可在相应的处理周期不变的情况下可将并行处理的数据率提高到原数据率的8倍。

4 FPGA仿真测试

在OuatusⅡ5.O平台上采用Verilog编写编解码器代码,测试步骤为:分析与综合;生成功能网表;配置输入信号波形;功能仿真;整体编译;时间仿真。

4.1 系统性能测试

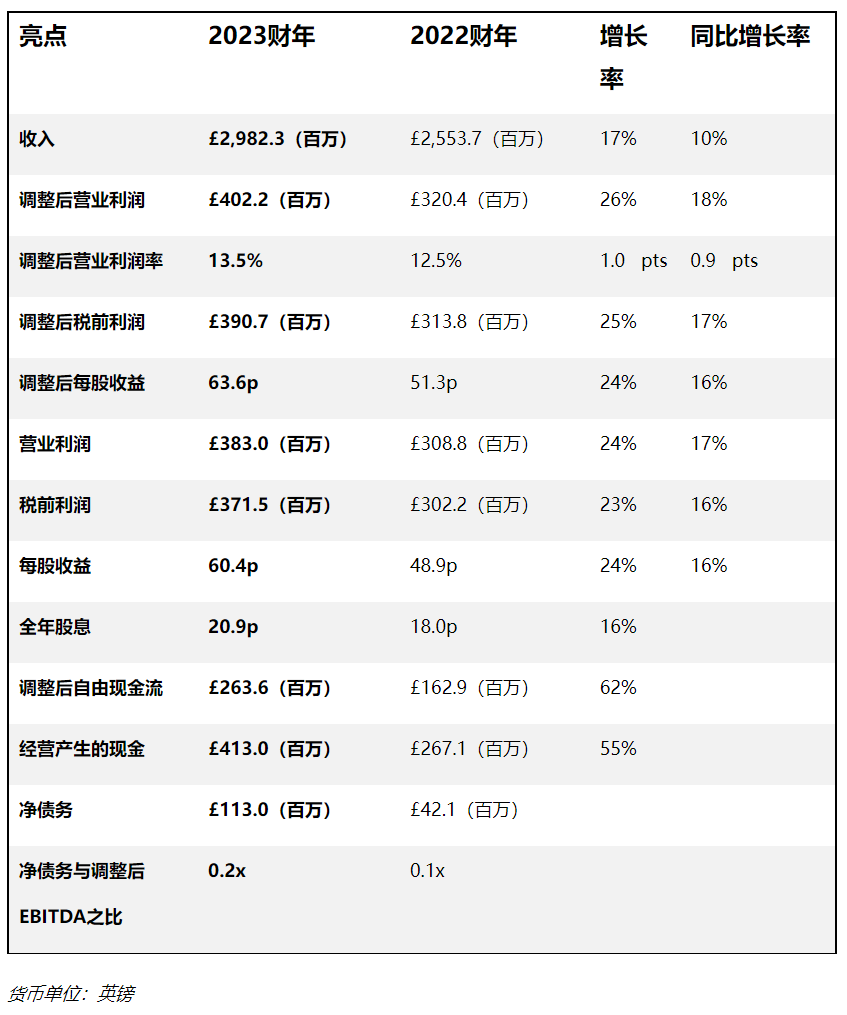

(1)资源利用率综合功能仿真和时间仿真的编译报告,系统占用资源详细情况如表1所示。

(2)解码数据率解码数据率=每帧数据的字节数×解码频率/系统所需周期。采用Ahera公司的RS解码器的IP器件,使用CycloneⅡ器件,其解码数据率为104 Mb/s。由该设计的时序仿真表明解码器8路复用后的解码数据率高达116.65 Mb/s。

(3)纠错能力及纠错仿真纠错能力由码型、解码算法、控制信号、时钟等因素共同决定,该设计的单路数据输入解码器最大纠错能力为7字节/204字节(每帧数据204字节,纠正随机错误7字节),接近RS码的纠错上限8字节/204字节。8位输入数据发生错误:02H~09H变成了01H,经系统纠错得到正确的输出波形。

4.2 系统构造

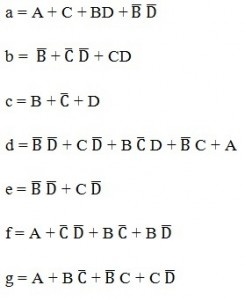

(1)查表法代替复杂的求逆单元为了获得更高的解码速率,使用更少的FPGA资源,系统设计使用标准基到复数基的变换与逆变换,用复数基进行乘法器设计,除法器设计是把处理数据从标准基转化为指数幂的表示形式,改用高效查表法代替复杂的求逆单元,将σ(x)的逆单元按照寻址方式转换为表格形式,在程序中直接调用,简化设计,提高了解码频率。

(2)并行流水线结构 由于传统设计是利用SC模块求解伴随式,KES模块求解关键方程,CESS模块求解错误位置和错误值,它们之间的处理周期差距很大,造成周期的极大浪费。而采用时分复用的流水线结构可有效解决这一问题,对结构简单的模块进行复用,在处理周期基本不变的情况下,从而提高并行处理的解码数据率。

5 结语

RS编解码器应用于诸多系统,例如:在数据传输链路应用中,可在SAN DHB和SAN Target上安装高速并行RS解码器,提高远距离光纤存储系统的可靠性;将RS纠错码应用于突发错误率较高的网络,并与高速的RAID的存储体系相结合,弥补由于使用RS编码器产生的延迟,从而实现网络存储系统的安全性和高速性。

矢量控制相关文章:矢量控制原理

评论