高速DSP系统的电路板级电磁兼容性设计

随着高速DSP技术的广泛应用,相应的高速DSP的PCB设计就显得十分重要。由于DSP是一个相当复杂、种类繁多并有许多分系统的数、模混合系统,所以来自外部的电磁辐射以及内部元器件之间、分系统之间和各传输通道间的串扰对DSP及其数据信息所产生的干扰,已严重地威胁着其工作的稳定性、可靠性和安全性。据统计,干扰引起的DSP事故占其总事故的90%左右。因此设计一个稳定、可靠的DSP系统,电磁兼容和抗干扰至关重要。

本文引用地址:http://www.eepw.com.cn/article/151410.htm1 DSP的电磁干扰环境

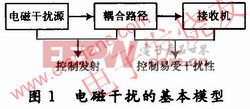

电磁干扰的基本模型由电磁干扰源、耦合路径和接收机3部分组成,如图1所示。

电磁干扰源包含微处理器、微控制器、静电放电、瞬时功率执行元件等。随着大量高速半导体器件的应用,其边沿跳变速率非常快,这种电路可以产生高达300 MHz的谐波干扰。耦合路径可以分为空间辐射电磁波和导线传导的电压与电流。噪声被耦合到电路中的最简单方式是通过导体的传递,例如,有一条导线在一个有噪声的环境中经过,这条导线通过感应接收这个噪声并且将其传递到电路的其他部分,所有的电子电路都可以接收传送的电磁干扰。例如,在数字电路中,临界信号最容易受到电磁干扰的影响;模拟的低级放大器、控制电路和电源调整电路也容易受到噪声的影响。

良好的电路板布线在电磁兼容性中是一个非常重要的因素,一个拙劣的电路板布线和设计会产生很多电磁兼容问题,即使加上滤波器和其他元器件也不能解决这些问题。

正确的电路布线和设计应该达到如下3点要求:

(1)电路板上的各部分电路之间存在干扰,电路仍能正常工作;

(2)电路板对外的传导发射和辐射发射尽可能低,达到有关标准要求;

(3)外部的传导干扰和辐射干扰对电路板上的电路没有影响。

2.1 元器件的布置

(1)元器件布置的首要问题是对元器件进行分组。元器件的分组原则有:按电压不同分;按数字电路和模拟电路分;按高速和低速信号分和按电流大小分。一般情况下都按照电压不同分或按数字电路与模拟电路分。

(2)所有的连接器都放在电路板的一侧,尽量避免从两侧引出电缆。

(3)避免让高速信号线靠近连接器。

(4)在元器件安排时应考虑尽可能缩短高速信号线,如时钟线、数据线和地址线等。

2.2 地线和电源线的布置

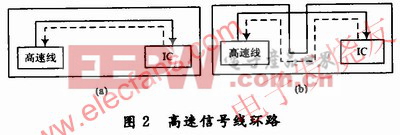

地线布置的最终目的是为了最小化接地阻抗,以此减小从电路返回到电源之间的接地回路电势,即减小电路从源端到目的端线路和地层形成的环路面积。通常增加环路面积是由于地层隔缝引起的。如果地层上有缝隙,高速信号线的回流线就被迫要绕过隔缝,从而增大了高频环路的面积,如图2所示。

图2中高速线与芯片之间进行信号传输。图2(a)中没有地层隔缝,根据“电流总是走阻抗最小的途径”,此时环路面积最小。图2(b)中,有地层隔缝,此时地环路面积增大,这样就产生如下后果:

(1)增大向空间的辐射干扰,同时易受空间磁场的影响;

(2)加大与板上其他电路产生磁场耦合的可能性;

(3)由于环路电感加大,通过高速线输出的信号容易产生振荡;

评论