基于闪烁存储器的DSP并行引导装载方法

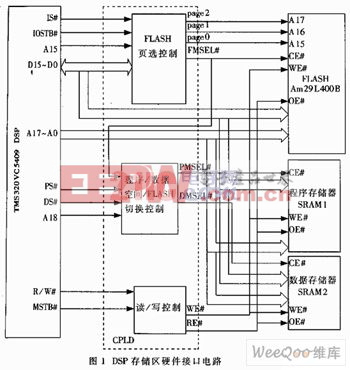

2 硬件电路组成

DSP 存储区硬件接口电路如图1所示。主要由5部分组成:DSP处理器-TMS320VC5409、系统逻辑控制电路(采用CPLD-EPM7128实现)、闪存FLASH-Am29LV400B(256K字的FLASH用来存储应用程序和初始化数据)、程序存储器SRAM1-IDT71V416S12PH(容量为256K字)、数据存储器SRAM2-IDT71V016S12PH(容量为64K字)。逻辑控制电路主要由3个模块组成:FLASH页选控制模块、读/写控制模块、程序空间/数据空间/FLASH切换控制模块。图中,CPLD的输出FMSEL为FLASH的片选脚;PMSEL为程序空间的片选脚; DMSEL为数据空间的片选脚。

FLASH分为8页,每页32K,通过CPLD中的FLASH页选控制模块(Page0~Paeg2)实现FLASH翻页功能。为实现FLASH引导装载,FLASH物理空间的前32K映射到TMS320VC5409的数据空间0x8000h~0xFFFFh上,即TMS320VC5409的数据空间 0x8000h~0xFFFFh为FLASH的前32K空间。为了重点说明FLASH的引导装载过程,本文只谈及DSP片内程序存储空间以及FLASH前 32K字的使用情况。

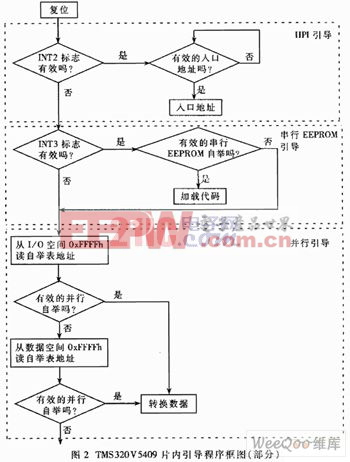

TMS320VC5409芯片具有两种引导方式:片内引导方式和片外执行方式。片内引导方式就是利用片内ROM中的引导程序将程序从外部加载到程序存储器中运行。由于FLASH的速度较低,难以与DSP相匹配,因此,本文采用片内引导方式。

TMS320VC5409 片内掩模ROM中固化的引导装载(Bootloader)程序用于在上电复位时把用户程序从外部引导到高速RAM中,以保证其全速运行。 TMS320VC4509提供的片内引导方法有:有机口HPI方法、8位或16位并行EPROM方法、8位或16位并行I/O方法和8位或16位串行口方法等。TMS320VC5409片内引导装载源程序可以在TI网络下载得到,读者可以自行分析。下面通过图2所示的引导过程框图,阐述一下本文选用的并行引导方式过程。

评论