Altera器件时间匹配问题的解决方案

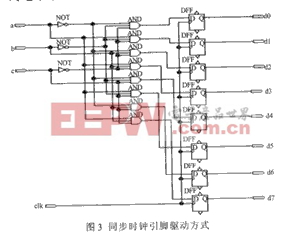

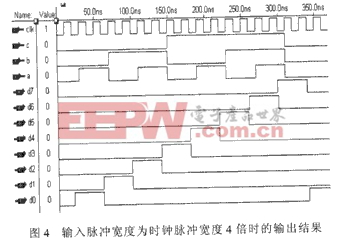

对于三到八译码器而言,用a、b、c表示输入引脚,d0、d1、d2、d3、d4、d5、d6、d7 表示三到八译码器的输出引脚。对该设计项目进行编译后模拟仿真,这时非常容易从模拟仿真出来的波形上看到出现了毛刺。如采用同步时钟(引脚驱动)方式,就可以消除毛刺。要注意的一点是建立和保持时间(Setup/hold time )是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间Set up time。如不满足Setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。hold time不够,数据同样不能被打入触发器。我们选用a端的输入脉冲宽度是时钟脉冲的四倍,这样D 触发器就可以正常动作,输出结果是正确的,见图3、图4。如果我们一定要使输入脉冲等于输出脉冲的宽度,就要使输入脉冲的高电平与时钟脉冲的高电平错开,保证D触发器能工作。

|

|

评论