利用FPGA加密芯片的抗DPA攻击电路设计

1.3 预充电技术的实现

普通逻辑门不能提供持续转换活动,逻辑门的输入不变将导致门的数据独立。解决这个问题要通过增加预充电电路来提供变换。当时钟为高时,连接预充电电路输入一个预充电相位,连接点变化到逻辑O;当时钟为低时,电路输入计算相位,实际计算完成。在FPGA上采用预充电逻辑的目的是要求在预充电相位期间slice的输出必须是逻辑O,有两种方式来完成。在一个Xilinx的slice中,每个LUT后跟着专门的多路选择器和内存单元,可配置为寄存器或锁存器。这里考虑使用多路复用器和内存单元来实现预充电,每种方法各有优点和缺点:

(1)使用时钟控制的多路复用器来实现预充电功能。将每个片子中单独的内存单元作为寄存器,但是除了寄存器的普通时钟还要分配一个反向时钟。这种方法的缺点是复制一个时钟信号并生成直接和互补信号将明显增加功耗和电路面积,布线也将复杂化。

(2)使用内存单元作为带有反向使能输入的异步清零锁存器来实现预充电功能。只需要一个单独信号给寄存器和预充电锁存器,预充电功能由连接反向使能输入和锁存器的清零输入实现,使用这种方法的缺点是专门设计的寄存器存储器需要一个单独的slice。

2 DES加密模块的实现

要在FPGA上实现安全防护结构来确保关键部件的功耗恒定。这里选择从双轨和预充电技术在FPGA上实现旁路安全防护逻辑。当前的技术水平需要在FPGA上进行精确控制布局和布线。下面从S盒硬件宏的实现和DES加密核的实现来介绍基于FPGA的DES加密模块实现。

2.1 S盒硬件宏的实现

S盒的设计是DES算法关键部分,S盒设计的优劣将影响整个算法性能。在采用FPGA实现时,应从资源和速度的角度出发,有效利用FPGA可配置属性,充分考虑器件内部结构,尽可能使两者都达到最优。在设计中,由于综合工具的介入,所输出的网表很难被设计者所理解,同时要找到一种更好的方法来控制组合电路,因此要建立硬件宏模块,简称硬宏。这与传统的设计流程不同之处是要充分利用:FPG Editor的功能,目的是从FPGA底层结构的配置上实现双轨和预充电技术。

通过Xilinx提供的FPGA Editor工具,首先读入布局布线后输出的NCD文件,并将其转化为新的NVD文件,再送往BitGen软件,进行布局布线的优化,最终在FPGA内部来建立目标电路,把它存为一个宏文件便于在上层进行调用。要注意两个问题:建立硬宏需要进入到slice内部,准确控制Slice内部的器件选择和器件之间的连线,防止设计出错;宏的功能验证要建立仿真模型,直接编写一个行为仿真模型后在上层设计中调用这个仿真模型,要确保仿真模型和宏之间的一致性。

2.2 DES加密核的实现

DES算法的基本流程如下:首先,输入明文通过初始置换,将其分成左、右各为32位的两个部分,然后进行16轮完全相同的运算。经过16轮运算后,左、右半部分合并在一起经过一个末置换(初始置换的逆置换),于是整个算法结束。在每一轮运算中,密钥位移位,然后再从密钥的56位中选取48位。通过一个扩展置换,将数据的右半部分扩展为48位,并通过一个异或操作与一个48位密钥结合,通过8个S盒将这48位替代成新的32位数据,再通过一级置换操作,这四步操作即为函数f。

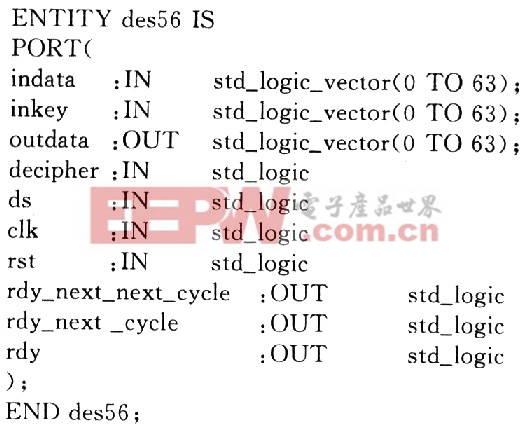

S盒是DES中的非线性模块,直接决定DES算法的安全性。在函数f的实现中,采用上面的思路,使用例化调用了S盒。DES加密核的VHDL设计思路如下:首先调用库函数构造ROM,然后使用VHDL语句进行行为描述。这种方法要结合器件的内部结构,对于小容量的ROM采用数组描述,大容量的ROM应采用元件的方式来实现。在VHDL设计中,库函数、子程序的调用以及元件的调用和使用间接变量,都是影响速度的主要因素。由此得到DES Core的接口定义如下:

评论