基于ARM920T设计的SMC接口研究与PC/104总线仿真

摘要:通过分析920T核ARM 处理器的高速片上系统总线AHB时序及其静态存储控制器SMC接口模型,研究IBM PC/AT和IEEE PC/104总线规范,提出一种在ARM 平台上实现兼容PC/104总线的方案.深入探讨两种平台体系在存储器结构、指令系统及总线时序等方面的巨大差异,给出了克服这些差异并实现总线功能兼容的方法.该兼容总线解决了在ARM 平台上无法使用标准PC/104模板的难题,采用该方案有利于在嵌入式系统的设计中兼取ARM 处理器和PC/AT体系的优势.

本文引用地址:http://www.eepw.com.cn/article/151214.htm引 言

PC/104 是一种专门为嵌入式应用而定义的工业控制总线规范.以IBM PC/AT总线规范为基础的个人计算机及其外围设备在应用上取得了巨大的成就,IEEE一996称之为ISA(工业标准架构:Industry Standard Architecture)总线.PC/104是ISA标准的延伸,定义在IEEE-P996.1中,称为兼容PC嵌入式模块标准.PC/104实质上是一种紧凑型的ISA,其信号定义和Pc/AT基本一致,但电气和机械规范却完全不同,是一种优化、小型、堆叠式结构的嵌入式总线系统.PC/104总线来自于实践发展的需要,同时得益于PC技术的迅速发展,由于其开发环境友好、兼容芯片丰富、标准支持广泛等优势,受到了众多从事嵌入式产品生产商和系统集成商的欢迎,尽管现在ISA设备已不常见,但PC/104在嵌入式系统领域却仍是通行的标准.

ARM是当前嵌入式系统应用中的热门技术.由于ARM处理器的卓越性能、较低的价格以及业内半导体厂商的广泛支持,在嵌入式环境中有广泛的应用.ARM 公司创造了CHIPLESS模式,该公司通过将高效的ARM 内核授权给半导体公司,由半导体公司根据实际的应用情况加上各种外围的功能电路来构成一块完整的芯片,这种模式使半导体厂商得以有能力生产功能强大的各种专用处理器芯片.AR M在设计上基于SoC思想,优先考虑对每一个具体应用使用最大可能集成周边设备的单一芯片,但在板极扩展方面仍然缺乏能被广泛接受的新工业标准.

1 PC/AT模型和PC/104总线

1.1 总线信号

PC/104_4 ]是一种16位总线,但可向前兼容8位XT模式,典型总线时钟为8 MHz,4个时钟脉冲可完成一次完整的总线访问,必要时可插入一个额外的等待周期以适应低速外设.在嵌入式系统开发中常用以下信号.

1.1.1 地址和数据信号线

BALE总线地址锁存使能信号线,由平台CPU驱动.当ISA扩展卡或DMA控制器占用总线时,它也被置为逻辑1.

SA~19:O>:低2O根地址信号线,由当前总线的拥用者驱动.

LAd 23:17> :锁存地址信号线,用来访问16MB的存储器地址空间.由当前总线拥有者或DMA控制器驱动.

SD15:0> :数据信号线.

1.1.2 总线周期控制信号线

MEMR#:存储器读信号线.

MEMW #:存储器写信号线.

IOR#:I/O I/O读信号线.

IOW #:I/O I/O写信号线.

1.1.3 中断和DMA(Direct Memory Access)信号线

IRQx:中断请求信号线.

DRQx:DMA请求信号线.

DACKx#:DMA应答信号线.

1.2 地址空间

PC/AT系统使用不同的指令访问存储器空间和IO端I:1空间,访问存储器空间时PC/104总线驱动MEMR#和MEMW#信号,访问存储器空间时PC/104总线驱动IOR#和IOW #信号.两个空间使用同一套地址线,但是由于端口空间只有64K有效,所以进行IO 端口访问时地址线上只有SA15:O>是有效的.

PC/AT系统有专门的端口访问指令用于实现端口访问,Linux用户程序只需以root权限调用ioperm()指定需操作的端口地址范围,之后即可自由访问这些端口.由于用于访问端口的一组宏实际上直接对应CPU的端口访问指令,所以存取效率很高.

1.3 PC/104总线周期

PC/104总线周期分为CPU驱动和DMA控制器驱动两大类,在嵌入式应用中较常用的是CPU驱动的IO读/IO写周期.

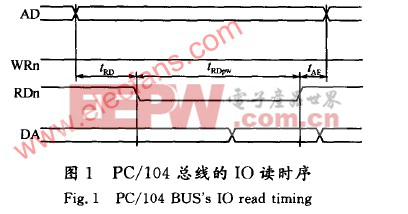

图1中采用8 MHz时钟的标准PC/104总线£Rd大于300 ns,tAF应大于250 ns,tRDpw约为500 ns。

评论