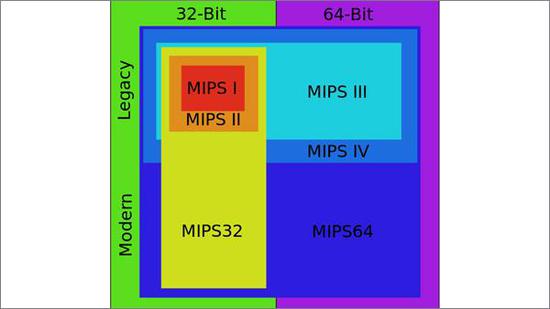

MIPS 体系和CISC体系结构有什么不同

(1)延迟分支:MIPS CPU的流水线结构意味著当一个跳转/分支指令到达执行阶段产生新的程序计数器值时,跟在跳转指令后的指令已经开始了,该体系结构并不是丢弃这部分有潜在用途的工作,而是要求紧跟分支后的指令总是在分支目标指令之前执行。紧接分支指令后的指令位置称为分支延迟槽。

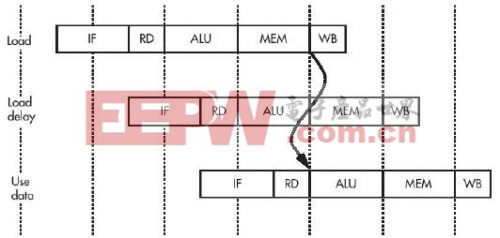

要是硬件没有特殊处理,是否分支的决定以及分支的目标地址,就会在ALU流水阶段结束时得到——到此时,如图1.3所示,已经太晚了,甚至在下下一个流水线槽都来不及提供一个指令地址。

但是分支指令的重要性足以给予特殊处理。从图1.3所示,提供了一条经ALU的特殊路径可以让分支目标地址提早半个周期到达。连同取指阶段多出来的半个时钟周期的偏移,就刚好来得及去除分支目标指令作为下下一个指令。这样硬件就会运行分支指令、接着运行分支延迟槽指令、然后是分支目标指令——再没有其它的延迟。

编译器系统或者汇编程序应该考虑甚至利用分支延迟;结果是通常有可能通过适当安排使得延迟槽中的指令做些有用的工作。经常可以把别处的指令一道延迟槽中。

对于条件分支问题会有点复杂,分支延迟指令应当对两条分支路径都无害。实在找不到有用的事情可做时,延迟槽中填入一条nop指令。除非明确要求,否则许多MIPS汇编器都对程序员隐藏这个古怪的特性。

图1.4:流水线和加载延迟

(2)数据加载延迟:流水线的另一个后果就是一条加载指令的数据在下一条指令的ALU阶段的开始才从高速缓存/内存系统到达——所以在下一条指令中不能使用加载的数据。

紧接加载指令后的指令位置称为加载延迟槽,一个优化的编译器将试图用它做些有用的事情。汇编器对程序员隐藏这一点,但可能插入一条nop指令。

在现代的MIPS CPU上,加载结果是互锁的:如果你试图过早使用结果,CPU将停下来等待数据到达。但是早期的MIPS CPU没有互锁,在延迟槽中试图使用数据将导致无法预料的结果。本文引用地址:http://www.eepw.com.cn/article/151202.htm

评论