基于CPLD和嵌入式系统的高速数据采集系统的设计与实现

2.2.7FIFO数据缓存电路

从图1可以看出,系统中包含两级FIFO。第一级FIFO芯片采用1片CY7C4251,容量为8KB×9bit,工作频率为100MHz。第二级FIFO采用2片CY7C4255并联,容量为8KB×36bit,但实际上只用了24bit数据宽度,因为8bit的A/D转换数据累加10000次,24bit就能满足系统的功能要求。

2.3软件开发

该数据采集系统的软件编程包括两部分,一部分是MPC860嵌入式系统的编程;另一部分是CPLD的编程。关于CPLD的编程模式见2.2.6,这里只介绍嵌入式系统的软件开发模式。

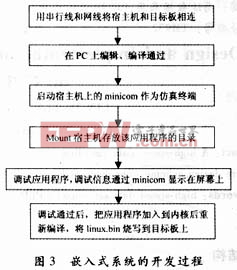

本系统采用交叉编译的方式进行Linux应用程序的开发和调试,先将应用程序在宿主机上调试通过后,再移植到目标板。这种模式适合于大型复杂的应用,优点是程序调试方便但移植需要做一些工作。其开发流程如图3所示。

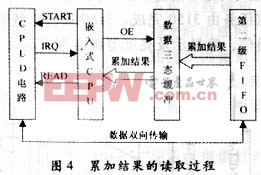

系统总的工作过程为:由MPC860发送一个START高电平给EPM3128,EPM3128接收到此信号后,产生2000个10ns的脉冲信号给ADC08200,采样后的数据存放在CY7C4251中。EPM3128产生CY7C4251的读脉冲依次读取FIFO中的数据并将其与从CY7C4255中取来的24位数据相加后再送回到CY7C4255中,每次累加在40ns中完成。这样循环10000次,就完成了数据的累加。累加完成后,EPM3128发送IRQ中断请求信号至MPC860,MPC860响应中断在IO口上产生READ低电平读信号,CPLD产生CY7C4255的读使能信号将数据读出送至三态缓冲器74F245,MPC860读取数据时发送OE信号选通数据三态缓冲器74F245将数据读出至MPC860数据总线,接收完数据通过 网口将数据发送给上位机处理。累加结果的读取过程如图4所示。

评论