基于DSP 的高速信号采集系统设计

3.3 CPLD 程序设计

CPLD 程序中要完成的有片选信号(包括一部分地址信号)和中断信号的逻辑处理,选用ALTRA 的EPM7032AE[5]。

DSP 的外部中断INT1 反映的是USB 中断请求,INT1 为低有效而USBINT 为高有效,INT1=NOT(USBINT);DSP 的RW 信号在读操作时为高电平在写操作时为低电平,MEMSTRB 存储器选通信号为低有效,SRAM 的写信号MEMWR 和读信号MEMRD 均为低有效, 故MEMWR=RW OR MEMSTRB,MEMRD=NOT (RW)OR MEMSTRB;DSP 的I/O 选通信号IOSTRB 为低有效, 而对于接受I /O 控制的USB 芯片来讲其读写信号RD 和WR 均为低有效,故IOWR=RW OR IOSTRB,IORD=NOT(RW) OR IOSTRB;DSP 的数据选通信号DS 为低有效,存储器选通信号MEMSTRB 也为低有效,而SRAM的片选信号RAMCS 同样为低有效,并且RAMCS在DS 或MEMSTRB 有效时均应被激活,RAMCS=MEMSTRB OR DS;3.4 上位机程序设计:

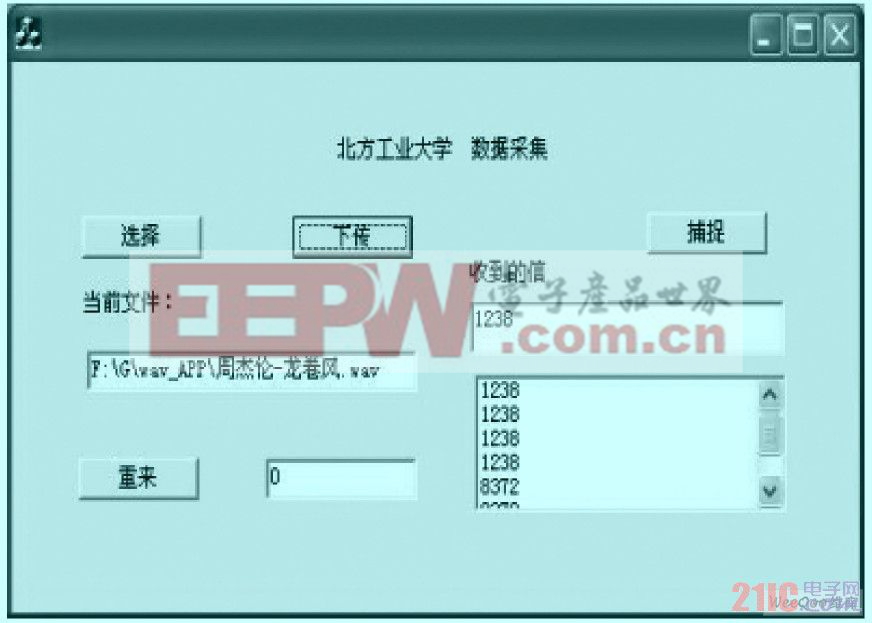

上位机程序的功能是接收来自下位机的传送数据和向下位机发送数据和命令,对于接受到的数据可以利用数据分析系统进行分析得出结果,而对于向下位机发送的数据工业中以控制参数和音频命令居多,故本设计中上位机界面提供了这些内容, 界面如图2 所示。

上位机界面

图2 上位机界面。

3.5 调试

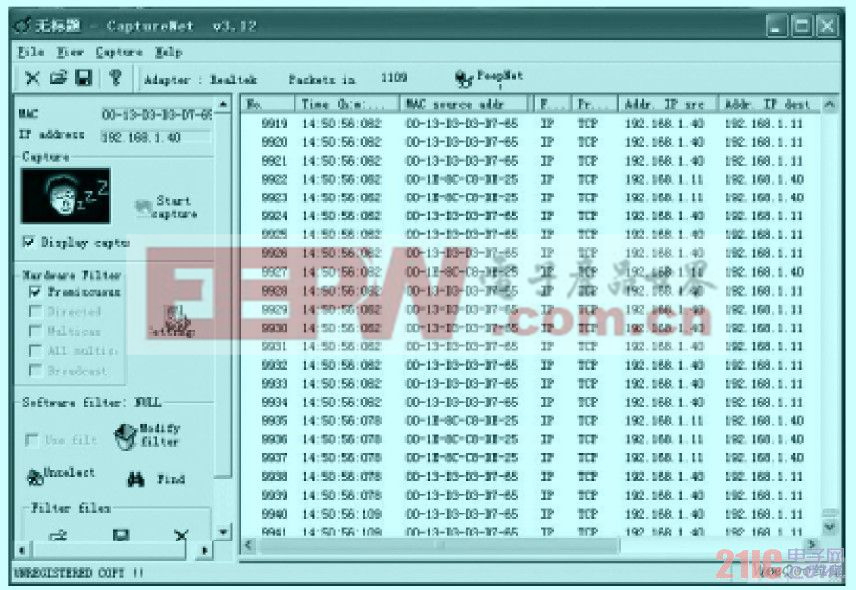

抓包测试图

图3 抓包测试图。

电路板制作完成后, 用联机网线将电路板和PC 机连接,将电路板IP 和PC 机IP 设置在同一组中,从PC 机发送包含0-20kHz 各个频率的音频信号给DSP,DSP 将该音频通过AIC23 后播放,与PC 机同步播放的音频信号相对比检查传输实时性, 对比其各部分频率或对比PC 机内和DSP 内数据数值可知数据传输质量如何。同时DSP 将采集到的信号发送给PC 机,由于数量很大全部显示反应迟缓所以捕捉显示,对比CCS 查看到的DSP内存储数据可知传输是否正确,用网络抓包软件抓包可以清楚的看到通信的内容, 如图3 所示。

4 结束语

系统设计完成后通过测试能够完成高速信号的采集和传输, 数据传输正确, 质量良好。数据传输的实时性和可靠性达到用户的设计要求。在该系统的设计中,DSP 的强大运算能力和扩展的数据存储空间为复杂算法的实现提供了条件。在铝电解工业应用中,后续课题中将把电解铝控制的复杂神经网络算法写入到本设计的DSP 中,届时该设计的功能可将现场信号采集实时运算及控制以及上传下载高速信号集于一身。此外,在其它工控场合本设计也可扮演重要角色。本文引用地址:http://www.eepw.com.cn/article/151064.htm

评论