基于嵌入式技术的靶场破片测速系统设计

摘要:为了增强靶场破片测速系统的便携性和实时性,提出了一种基于嵌入式技术的靶场破片测速系统设计方法。系统硬件上采用ARM+FPGA的架构,软件上不仅采用Qt/Embedded设计了图形界面,而且给出了嵌入式设备上Qt/Embedded程序的优化方法。经过多次野外破片测速试验检测,系统工作稳定,可实现破片飞行速度、速度降、末速度、破片速度分布等参数的获取。试验结果证明,系统能够满足靶场破片测速的大多数需要。

关键词:嵌入式技术;破片测速;ARM;FPGA;Qt/Embedded

0 引言

破片速度是战斗部爆炸效能评估的一个重要参数。传统的靶场破片测速系统多使用多路数据采集卡设置好的参数现场采集标靶的试验波形,试验完成后再交由计算机进行后期处理和解读以获取破片速度等参数。但随着军事科技的日新月异,靶场破片测速系统需要根据实际情况现场设置的参数越来越多,参数设置的灵活性越来越强,对系统工作的实时性要求越来越高;另一方面,战斗部爆炸试验在野外进行,条件恶劣,大型设备携带不便,以往的PC机+数据采集卡设计已经越来越不能满足靶场试验的要求。嵌入式系统具有功耗小、便携性好、稳定性高、实时性强的特点,近年来随着嵌入式技术的不断发展,把嵌入式技术引入靶场破片测速系统设计中,为靶场破片测速系统设计提供了一个新的思路。

本文设计的靶场破片测速系统以ARM处理器为控制核心,利用了FPGA强大的多路并行处理能力进行数据处理,在基于嵌入式Linux的平台上采用Qt/Embedded设计了友好的人机交互界面。系统功能完善,操作直观简单,携行方便,能够满足在野外进行破片测速的大多数需要。

1 系统硬件设计

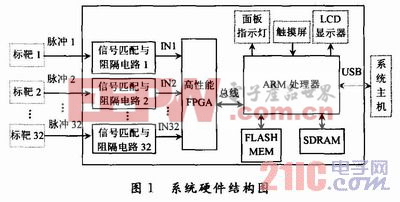

系统使用ARM+FPGA的设计方式。

ARM处理器选用Samsung公司推出的基于ARM920T内核的S3C2440。S3C2440主频高达400 MHz,完全能够胜任系统工作要求。S3C2440集成了SDRAM和FLASH控制器,提供了串口,触摸屏接口,USB接口等多种接口,接口丰富、功能强大,是一款高性能,低价格的处理器,在嵌入式设备中获得了广泛的应用。

FPGA(现场可编程门阵列)选用了Altera公司StratixⅡ系列的EP2S15芯片,该芯片器件密度可达到15600等效逻辑元(LE),能提供419Kb片内TriMatrix存储器,多达12个DSP区块共有48个(18×18 b)乘法器,用来实现高性能滤波器和其他DSP功能。支持多种高速外接存储器接口,支持各种标准的I/O,高速差分I/O,具有强大的高速多通道并行处理能力。

系统使用该芯片64 MB SDRAM作为系统内存,64 MB FLASH用于Linux内核、文件系统、应用程序和试验数据的存储,为系统运行提供了充足的存储空间。

系统硬件结构图如图1所示。

在图1中,系统采用了32个标靶用于破片测速,一个标靶对应FPGA的一个通道,每个通道对应一个32 b计数器。战斗部爆炸后,破片击穿标靶时产生的脉冲将作为起停信号,控制FPGA中相应通道的计数。所有通道中最早触发的通道为基准通道,相应通道计数器值为0。从基准通道被触发时刻起,除基准通道外所有通道计数器开始计数,直到本通道收到触发信号或者最长计数时间时停止计数。停止计数时的通道计数值即为本通道的触发计数值。

FPGA设置了32通道通断寄存器、32通道输入触发器、通道触发计数器等多个数据寄存器,用于保存标靶的通断、触发状态及各个通道的触发计数值;设置了最长记录时间寄存器等多个控制寄存器用于控制FPGA的动作。经过处理,FPGA将标靶的通断、触发状态及最终触发计数值写入相应数据寄存器中。

评论