基于Microblaze软核的嵌入式系统设计

摘要:结合实际项目的开发经验,详细讲解了基于Xilinx Microblaze软核开发的整个流程,包括硬件平台搭建、软件平台开发、嵌入式操作系统的加载以及用非易失性存储设备对FPGA进行上电配置等内容。利用FPGA软核进行嵌入式系统开发,将得到越来越多的关注和应用。

关键词:嵌入式系统;软核;片上可编程系统;可编程逻辑门阵列

引言

近十年来,FPGA行业获得了突飞猛进的发展,其在系统开发工作中的地位已从简单的胶合逻辑上升到了数字系统的核心处理器件。可编程片上系统SOPC(Systern On Programmable Chip)将CPU核与外设核以及系统软件集成到单一芯片中,帮助用户快速“量身定制”所需要的产品,创造性地为用户提供了基于FPGA的嵌入式设计方案。

Xilinx公司作为FPGA嵌入式软核解决方案商,在其所有系列的FPGA中提供了Microblaze 32位软核处理器,并推出了用于嵌入式系统编程的EDK(Embedded Development Kit)集成开发解决方案。本文结合实际项目的开发经验,详细讲解了基于Microblaze软核开发的整个流程,包括硬件平台开发、软件平台开发、嵌入式操作系统的加载以及用非易失性存储设备对FPGA进行上电配置等内容。

1 Microblaze的体系结构

Microblaze处理器采用RISC架构和哈佛结构,在时钟频率为150 MHz的情况下可以达到125 DMIPS的性能,该处理器(版本7.30)具有以下一些特征:

①32个32位通用寄存器和最多18个专用寄存器;

②32位指令系统,支持3个操作数和2种寻址方式;

③分离的32位指令和数据总线;

④通过本地存储器总线LMB直接访问片内的块存储器BRAM;

⑤具有高速的指令和数据缓存Cache,5级流水线结构;

⑥自带硬件调试模块MIDM;

⑦带有8个主/从快速单工链路接口。

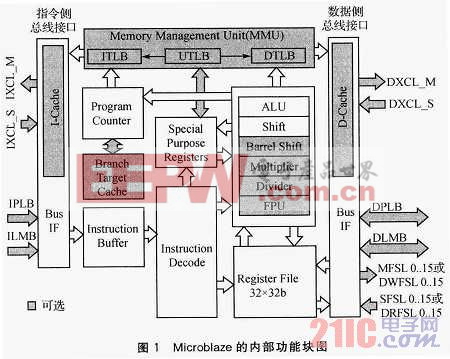

图1给出了Microblaze的内部功能块图。

从图1可以看出,Microblaze软核与其他专用集成芯片的硬CPU核在结构上没有大的差别,但它却可以通过PLB总线(Processor Local Bus )与EDK软件包将自带的各种软外设进行按需连接,并且支持用户自定义IP通过PLB总线(Microblaze从7.30版本开始取消了原有的OPB总线)和FSL(Fast Simple Link)总线与Microblaze软核连接,从而最大限度地发挥FPGA设计的灵活性。

评论