实现8位微控制器升级至32位的关键

现今基于嵌入式微控制器 (MCU) 的应用对功能的要求不断增多,例如,电机控制必须具有更高的能源效率;以往独立的应用也必须联网。在这种情况下,对微控制器的性能和存储容量的要求也大为提高。对一些应用而言,解决的方法就是从8位或16位MCU升级至32位。这样一来,虽然性能得以提高,但也可能导致单元成本、系统复杂性以及软件开发成本的增加。本文将讨论如何通过系统集成将8位功能加入至32位系统中,以及提供功能强大的低成本开发工具,从而加快这种升级过程。

本文引用地址:http://www.eepw.com.cn/article/150823.htm通过提升制造技术可以降低单元成本。不过,除非32位MCU具备和8位或16位系统相若的系统集成度,否则这些优点都将因为加入外部器件的成本而一笔勾销。高性能系统独有的高速缓存等往往令系统变得复杂。但是对那些正在升级至 32 位系统的典型实时控制应用而言,这些并不是必需的功能。虽然,把现有代码移植到新一代更高性能微控制器的成本是无法省去的,但为了减少整体所需的工作量,可以通过开发工具的设计来推动这种升级过程。

市场趋势:转向32位MCU

根据Gartner Dataquest公司统计,在过去10年间,32位微控制器在MCU市场的营业额从零开始增长到了近25%,目前的增长率高于8位或16位系统。而且,随着众多配备了针对特定市场领域,如汽车市场等的功能集的器件不断涌现,MCU 市场正在逐步分化。 从8位和16位MCU升级至 32位架构的重点是深度嵌入式实时控制应用。

此外,目前产业界还出现了一个明显趋势,就是ARM RISC处理器正逐渐成为32位MCU的行业标准,一如当初8051架构是8位系统的标准。目前,ARM 在32位嵌入式RISC MCU市场的占有率达 75%,截至2005年1月,ARM各合作伙伴已付运超过25亿片的的ARM 内核的MCU。

成本:技术和整合度的考虑

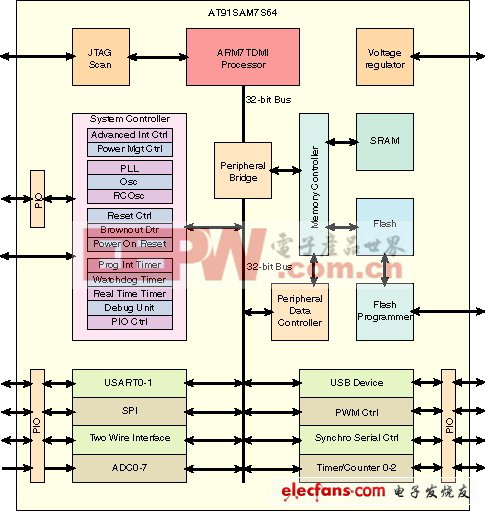

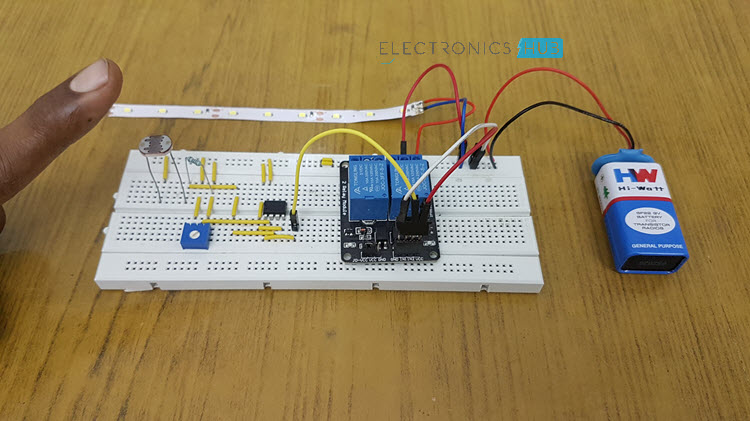

采用当前0.18μm的工艺技术,生产一块包含有一个32位RISC处理器、标准外围设备和一个小容量闪存的单芯片成本并不昂贵,但对于8位应用而言,单凭此尚不足够。从8位微控制器升级的应用需要有更高水平的系统集成度 (见图1),来满足整体的系统成本预算。而且,这种整合度必须让32位系统具有8位片上系统的基本功能。

32位器件必须采用单电源工作;集成大电流驱动 I/O 和收发器;控制系统上电;通过低成本晶振生成系统时钟;而且其 I/O上应具有可编程上拉电阻 (pull-up)。此外,32位器件还应确保在任何环境下应用的行为都可以预测,这需要一个节电检测器 (brown-out detector)、一个可编程监视器,以及一个集成RC振荡器,而毋需高速缓存和闪存加密位 (lock bit)。

从8位升级至 32位系统时的性能要求

嵌入式闪存的访问时间

基于8位微控制器的应用一般是以控制为主导 (control-driven) 的,要求对外部事件的确定过程式 (deterministic) 响应和可预测的响应时间。然而,用来加快对缓慢非易失性储存媒介之存取速度的高速缓存却不是决定性的,因此对于那些对时间要求严格的应用来说是不可接受的。提高实时性能又不增加成本的惟一方法,就是加快对嵌入式闪存的存取速度。

目前产业界的0.18μm工艺技术能在30MHz的ARM微控制器上进行单周期内访问,原始性能可达27MIPS,远高于现有的一般 8位微控制器。

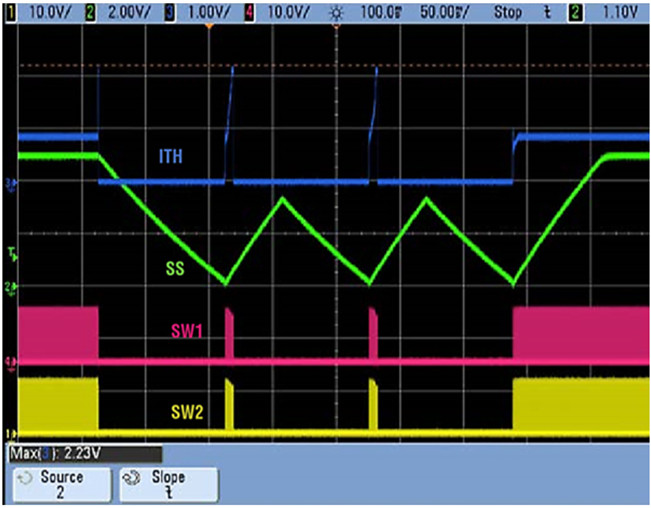

提高中断处理能力

实时控制应用一般是采用中断驱动,利用多个中断源和规定每一中断时间内所需的响应来进行。基本的ARM架构有一个弱点,就是它的中断处理机制很简陋,没有中断优先所需的硬件装置。这时便需要一种装置来增强中断能力,如图2所示。它提供一组带有 8 个优先级别之可独立屏蔽的向量式中断源。永久存储在SRAM中的基本中断处理程序负责分配中断的优先级级别,然后执行一条指令,利用中断号 (每一中断源均获发一个独有编号) 作为偏移量 (offset),把用于所需中断服务程序的向量直接装载入程序计数器 (Program Counter)。这种简单有效的机制能够确保在最少数目的指令周期内,把控制传送到所需的中断服务程序中。

评论