基于Nios II的UART与PC间的数据通信

Nios II系列嵌入式处理器使用32位的指令集结构ISA,完全与二进制代码兼容,它是Altera公司的第二代软核嵌入式处理器,性能超过200DMIPS。允许设计者在很短的时间内构建一个完整的可编程芯片系统,风险和成本比中小规模的ASIC小。这种开发方式特别适合设计针对网络、电信、数据通信、嵌入式和消费市场的各种嵌入式应用。

本文引用地址:http://www.eepw.com.cn/article/150764.htm本文基于以上这些特点,从硬件和软件两个方面探讨了基于Cyclone II系列EP1C12Q240C8与PC的通信方案。

1 串行异步通信的硬件接口

通用异步收发器,简称UART,能把字符的并行代码变换成串行代码发送出去,而且也能把这种格式的串行代码接收下米,并且转换成相应的并行代码。串行异步通信协议中字符代码传输格式如图1所示。在没有传送代码时,通信线会一直处丁逻辑1状态,而传送时,数据两头必须加上起始位和停止位。起始位总是逻辑0状态。停止位总是逻辑1状态,其持续时间可选为1位、1.5位或2位。数据的低位在前,但根据不同的编码规则,数据可能有5位、6位、7位或8位。图1中的校验位可根据需要选择奇校验、偶校验或不要校验位。

1.1 UART内核综述

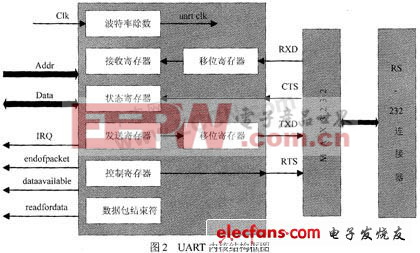

AVALON总线是一种结构相对简单的总线,用于连接NiosⅡ和其他外设。它规定了主从部件间的端口连接关系,以及部件间通信的时序关系。AVALON总线拥有多种传输模式,以适应不同外设要求。基本传输模式是在主从外设之间进行单字节,半字或字的传输。AVALON总线还支持一些高级传输模式,例如支持流操作,支持延时操作, 支持多个主设备同时访问。带Avalon接口的UART内核为Altera FPGA上的嵌入式系统合外部设备提供了串行字符流的通信方式,内核执行RS-232协议时序,由于大部分Altera FPGA系列上的I/O引脚不遵循RS-232电压电平规范,如果通过RS-232连接器的信号直接与FPGA相连,可能会损害器件。为了满足RS-232信号电平要求,在FPGA I/O脚和对应得RS-232外部接头间需要连接一个外部电平转换器。UART内核结构框图如图2所示,在UART内核和RS-232连接器之间采用Maxim公司生产的MAX3232型收发器。

UART发送器包括发送数据寄存器Txdata和相应的发送移位寄存器。Avalon主控制器通过Avalon从控制器端口写数据到发送数据寄存器。在当前不进行串行发送移位操作时,发送移位寄存器自动从发送数据寄存器中转入数据。发送移位寄存器直接连接到TXD输出。数据最低有效位先从TXD移出。发送数据寄存器和发送移位寄存器提供双重缓冲。主控制器可以在前一个字符正在移出时将新数值写入发送数据寄存器,并可通过读出状态寄存器的发送准备好位TRDY、发送移位寄存器空位TMT和发送溢出错误位TOE来监视发送器的状态。发送逻辑根据RS-232规范在串行TXD数据流中自动插入数量正确的起始位、校验位和停止位。

UART接收器包括接收移位寄存器Rxdata和相应的接收数据寄存器。Avalon主控制器通过Avalon从控制器端口读接收数据寄存器的数据。每当新字符完全接收后接收数据寄存器自动从接收移位寄存器装入数据。接收移位寄存器和接收数据寄存器提供双重缓冲。接收数据寄存器在后续字符正在移入接收移位寄存器时可以保持前面的接收字符。主控制器可通过读状态寄存器的接受准备好位RRDY、接收溢出错误位ROE、间断检测位BRK、校验错误位PE和帧错误FE位来监控接收器的状态。接收逻辑根据RS-232规范在串行RXD数据流中自动检测数量正确的起始位、停止位和校验位。接收逻辑检查接收数据中的4种异常隋况,并设置对应的状态寄存器位。

UART内核的内部波特率时钟来源于Avalon时钟输入,内部波特率时钟通过时钟分频器生成,除数值可以由系统指定,也可以由其寄存器中存器的16位值来决定,波特率和除数值之间的关系如下:

除数=int((时钟频率)/(波特率)+0.5)

波特牢=(时钟频率)/(除数+1)

分频器相关文章:分频器原理

评论