基于Linux的SoPC开发

SoPC(System on Programmable Chip)是一种特殊的嵌入式系统。首先,它是一种SoC系统,即由一个芯片完成系统的主要逻辑功能;其次,它是可编程的片上系统,即可配置、可裁减、可扩充、可升级,具有硬件系统的可编程性。采用SoPC的设计,具有很大的灵活性。

本文引用地址:http://www.eepw.com.cn/article/150696.htm它可以根据需要定制各个硬件模块,包括处理器、总线、存储器和通信模块等,这就使得在一个芯片上搭建一个按需定制的SoC系统成为可能。而Linux系统也因为其良好的可裁减、可配置的特点广泛应用于各种嵌入式系统,Linux操作系统提供了许多系统级的应用,例如网络协议的实现、进程调度、内存管理等,同时Linux是一个成熟的开源操作系统,有丰富的应用资源。利用这些资源和强大的系统功能,用户可以基于嵌入式Linux快速地开发出面向复杂应用的嵌入式系统。因此,结合SoPC和Linux优势,可以很好地满足嵌入式系统根据需求量体裁衣,去除冗余。本文给出基于Linux的SoPC应用系统的开发方法及一个具体的嵌入式应用开发实例。

1 硬件开发环境

1.1 开发平台

本文所采用的开发平台是AVNET公司生产的VIRTEX-II PRO FF1152开发板,它使用XILINX公司的Virtex-II Pro FPGA芯片XC2VP50-6FF1152C,同时开发板还有2个8MB×32的SDRAM存储器、2个RS232接口、一个以太网接口、1个LCD显示屏、8个LED灯,同时支持SPI-4.2的高速16bit LVDS接口、iSFP GbE光纤接口、System ACE接口以及一个P160标准的扩展模块[1]。

1.2 基于PowerPC的片上系统

XC2VP50-6FF1152C芯片内部含有两个IBM PowerPC 405核。PowerPC405是32位的RISC处理器,它采用IP植入架构的形式整合到XILINX公司的Virtex-II Pro FPGA器件中。

PowerPC硬核具有许多优点适合软件的开发设计[2]:具有三个定时器:即可编程的内部定时器、固定的内部定时器和看门狗定时器和灵活的存储管理和用于加强计算功能的乘法累加指令。PowerPC的强大功能可以胜任许多复杂应用系统对处理能力和运算速度的需求。同时,利用双核机制以及操作系统的进程调度可以大幅度地提高处理速度。

通过XILINX公司的EDK开发软件,可以很方便地在Virtex-II Pro系列芯片上搭建自己需要的硬件系统。处理器方面可以选择硬核IP:PPC405,或者软核IP:Microblaze;总线有OPB和PLB两种总线可供选择;同时,还有丰富的外围IP可以选择;在通信方面,分别有支持高速和低速的通信模块。支持高速的IP有:plb_etherne、opb_ethernet、opb_ethernetlite和plb_gemac等,支持低速的IP有:opb_iic、opb_spi、opb_uart16550和opb_uartlite等;在存储控制器方面,可选择的 IP有opb_sdram、opb_ddr、opb_emc、opb_sysace、plb_sdram、 plb_ddr和plb_emc等模块;其他方面还有支持中断、定时、GPIO、PCI等功能的IP模块。丰富的IP模块,加上可以利用IPIC(IP Interconnect)连接用户定制的IP,因而用户使用CPU时,不需要再另外使用一个SDRAM控制器芯片,或者另外使用一个以太网的控制芯片,极其方便。

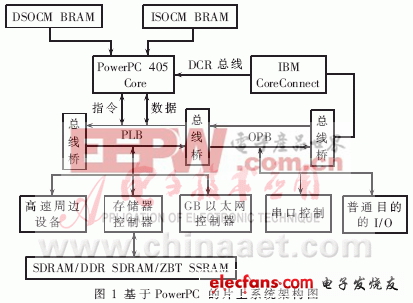

可编程片上系统由处理器、总线互连和外围设备等组成,典型的基于PowerPC的片上系统的架构如图1所示。

1.3 CoreConnect的总线结构[3]

总线互连是片上系统的一项关键技术。本系统采用了CoreConnect的总线结构。该总线结构是IBM公司开发的一种片上通信的总线互连技术。它的应用使得系统核、外设核、处理器核的复用、连接变得更加容易。这里,系统核是针对PLB总线上的功能IP模块的,而外设核是针对OPB总线上的功能模块的。CoreConnect总线互连是由本地逻辑总线PLB(Peripheral Logic Bus)、片上外围总线 OPB(On chip Peripheral Bus)、一个总线桥、两个判决器,以及设备控制总线DCR(Device Control Register构成的,其结构如图2所示。

评论