FPGA在锁相频率合成中的应用

累加器采用BCD码全加器。如要实现六位小数分频,每级累加器需三个八位锁存器和六个BCD码全加器。为了使电路设计相对简单,调制器部分采用吞脉冲技术。在采用三级累加器的情况下(参见图2),分频比最小时为N-3(第二级累加器-1有效,第三级累加器-2有效),最大时为N+4(图中三级累加器+1均有效)。因为是采用吞脉冲技术(不能添加脉冲),即在分频比为N-3时吞掉的脉冲最少。因此,在累加器全无溢出的情况下(分频比为N),应吞掉三个以上的脉冲,而这本不应吞掉的脉冲在整数分频部分予以添加。本设计采用无溢出时吞4个脉冲的方法,在三级调制器中的累加器的所有输出情况下会吞掉1~8个脉冲。整数分频计数器实际计数溢出值比分频值小4,以添加本不应吞掉的4个脉冲。

3 ∑-Δ调制器的FPGA实现

FPGA是80年代中期出现的高密度可编程逻辑器伯。FPGA及其系统软件是开发数字集成电路的最新技术,它利用计算机辅助设计,以电路原理图、高级语言、状态机等形式输入设计逻辑;它提供功能模拟、定时模拟等模拟手段,在功能模式、定时模拟都满足要求后,经过一系列的变换,将输入逻辑转换成FPGA器件的编程文件,以实现专用集成电路。

上述∑-Δ调制器采用三级累加器,实现六位小数分频。采用74系列的电路,需要约60片左右的集成芯片,电路板尺寸比较大,电路调试麻烦,可靠性差,很难推广使用和形成产品。将∑-Δ调制器用FPGA器件来实现,不但电路体积大大缩小,而且可靠性大大提高。使用FPGA器件的另一个好处是,可将同一系统中的其它数字电路纳入其中进一步缩小体积。

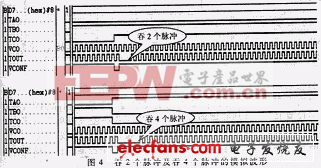

本设计的软件环境为Xilinx公司Foundation Serials 1.5i。采用原理图输入的设计方法,将复杂的原理图分块放在同一设计项目中,输入完毕后进行功能模拟,确认功能正确以后,对原理图进行编译并进行FPGA器件内部的布局布线,同时生成定时模拟数据文件。功能模拟主要是验证三级∑-Δ调制器的功能是否正确,判断的依据是看其是否可实现吞掉1~8个脉冲。图4是功能模拟的部分波形图,采用XC3064A-7-PC84芯片对设计进行布局布线,结果使用资源情况为CLB86%、IOB 27%、GCLK被使用。最高工作频率为4MHz。定时模拟能够保证功能正确。

在本设计中,将整数分频电路、吞脉冲电路均做在FPGA器件之中,进一步减小了电路板尺寸。

分频器相关文章:分频器原理

评论