G.723.1编译码算法的DSP实现

其中,τξ是一个中间参数,d是r〔n〕和h〔n〕之间的相关值,Φ是冲激响应的协方差矩阵。C、ε的计算:

对奇位置的码矢量,先把偶脉冲移一个样本位置,然后用上式计算。

3 算法实现

3.1 硬件设计

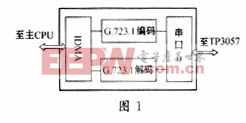

系统框图如图1所示。本文引用地址:http://www.eepw.com.cn/article/150508.htm

模拟的语音信号通过TP3057的A/D转换变为数字信号送入ADSP-2181(采样频率8kHz)。TP3057是美国国家半导体公司生产的A律编/解码器,它包含一个利用A/D和D/A转换结构的A律脉冲编码调制的编解码器/滤波器单片电路和一个串行PCM接口。其中,编码部分还包含一个可调输入增益的放大器、一个有源RC前置滤波器、自动调零电路、一个A率压缩编码器。解码部分包括一个A律解码器和截止频率为3400Hz的低通滤波器。前者从A律压扩的信号中重建模拟信号,后者校正译码器输出的sinx/x响应并滤除高频信号。

ADSP-2181是Analog Devices公司生产的一种性能优越的单片机,适合于高速的数字信号处理。 ADSP-2181除了三个运算单元、数据地址发生器和一个程序序列器,还含有两个串行口、一个16位的内部IDMA口、一个8位的BDMA口、一个可编程定时器、外部中断能力及片内程序和数据存储器。片内集成了80k字节的存储器,包括16k长度为24bit的程序存储器和16k长度为16bit的数据存储器。

利用IDMA口的自动接受发送功能,可以方便地实现ADSP-2181与主CPU间的数据交互。PC机通过IMDA口将程序装载入ADSP-2181内部存储器中。在ADSP-2181全速执行时,主机可以查询其状态,读取压缩后的码流,也可送入待解码的数据。

3.2 软件设计

软件设计包括三个模块:接口模块、编码模块和解码模块。

接口模块实现ADSP-2181与主CPU之间的数据交换。该模块包括DSP的主控程序和数据传输两部分。DSP的主控程序负责将采集到的语音数据分帧,送入编码器,并将接受到的码流分类后送入解码模块。数据传输部分负责采集数据和与主CPU的数据交换。

DSP程序根据ITU-TG.723.1标准定点算法,分为初始化(G723—Init)、编码(G723—Incode)、解码(G723—Decode)三个模块。

G723—Icode对包含240个采样点的一帧信号进行编码,返回12个或10个字长的二进制数据。

输入数据由串口得到,放在数组G723—Enc—Inp中,返回值放在数组G723—Enc—Out中,对于6.3kbps长工为12个字,对于5.3kbps长度为10个字。其格式按照G.723.1标准进行封装。

G723—Decode根据接收到的12字或10字打包数据重建240个语音样点。输入数据放在G723

Dec—Inp中,输出放在数组G723—Dec—Out中。

主机程序采用VisualC++编写,通过串口与DSP通信。

3.3 C语言的优化

开发中采用AD公司的集成仿真软件VisualDSP++,但是通常,C编译器能完成整个工作的70%,而30%的进一步优化必须通过手写汇编来实现。

3.3.1 循环展开

使用具有并行能力的DSP开发软件时,一个重要的思想就是充分利用DSP的字长和数目众多的运算单元,尽量把循环体展开。通过增加每次循环中执行的指令数来减少总的循环次数,可使得在同样的时钟周期内能运行更多的指令,提高了循环的效率。

3.3.2 提高寄存器的利用率

DSP芯片内部的运算单元运行效率非常高,但如果寄存器和数据总线之间的数据交换频繁,将使DSP的执行效率大打折扣。因为DSP在进行内存操作时,往往需要若干周期的延迟,如Load指令要有4个周期的延迟,Store指令需要2个周期的延迟。为了减少耗时的内存操作,可以在程序进入循环体之前,将要频繁使用的数据预先放入寄存器,然后反复调用,实践证明这种方法可以提高一部分效率。

4 实验结果

所有代码全部通过了ITU-T测试矢量的测试。

测试结果表明,对于高码率(6.3kbps)所需计算量为24.8MIPS,对于低码率(5.3kbps),所需计算量为21.3MIPS。该实现可以在IP电话、视频会议中得到广泛应用。

评论