一种自适应波束形成算法实现

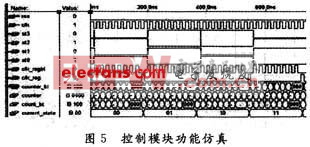

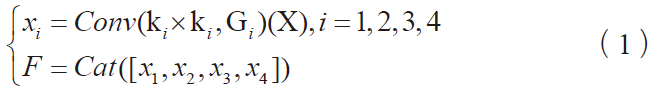

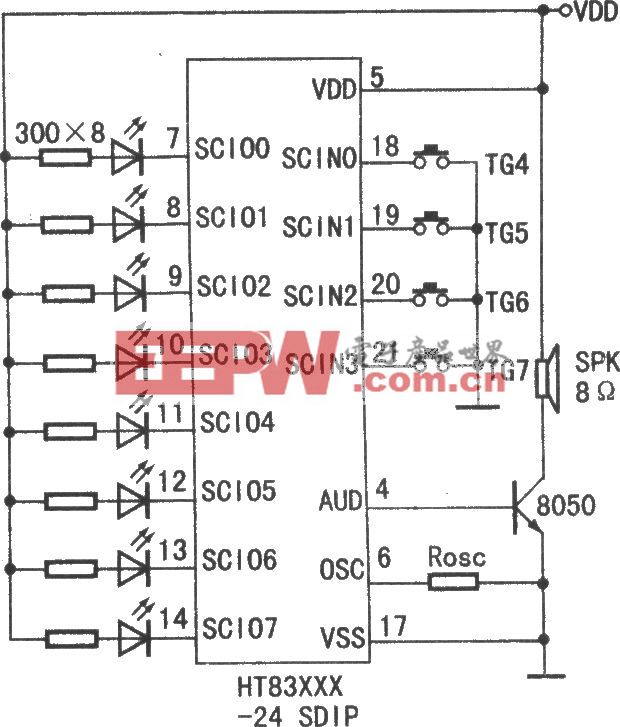

输入信号和权值是8位的复数数据,通过控制模块选择乘法操作的操作数,两个复数信号相乘的4种组合00,11,01,10可以完成实部和虚部之间4个乘法运算,四种情况控制模块输出的控制信号分别为ST0,ST1,ST2,ST3。

其中,clk_regbt用来控制乘法器完成乘法,counterbt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

2.2.2 存储模块

一种存储模块,它包括:用于根据外部指令/地址信号来产生内部信号的指令/地址寄存器,且所述的指令/地址寄存器件带有一个输出晶体管;被分成第一和第二两组的多个存储器件;用于连接所述的指令/地址寄存器件和所述的存储器件的布线;和用于安装所述的指令/地址寄存器件和所述的存储器件的基板;所述的布线包括:从所述的指令/地址寄存器件延伸至第一个分支结点的第一段布线;从第一个分支结点延伸至第二个分支结点的第二段布线;从第一个分支结点延伸至第三个分支结点的第三段布线;从第二个分支结点分出延伸至所述的第一组存储器件的第四段布线;和从第三个分支结点分出延伸至第二组存储器件的第五段布线;和所述的指令/地址寄存器件包括:阻抗调节器,用于调节从所述的指令/地址寄存器件和第一段布线之间的连接点看去所述的指令/地址寄存器件的输出阻抗,通过调节该阻抗调节器,可使所述的输出阻抗在内部信号的工作电压范围内基本保持不变;和上升时间/下降时间调节器,用于将内部信号的上升时间和下降时间调节至特定值。

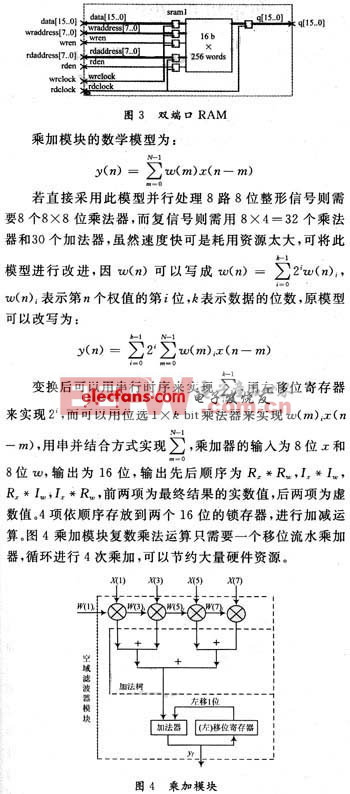

存储模块采用8位和16位双口RAM(如图3所示)作为信号数据和权值数据的存入和读取存储器,分别用来存放输入信号x、权值ω和误差e,分别由控制信号clkregbt,clk_regw和clk_rege来控制信号的写入和读出。其中x_ram用来存放输入信号;w_ram存放权值,其输入为系数更新模块的输出,输出为更新后的权值。

2.2.3 自适应处理及复数乘加器模块

数字波束形成器是通过加权因子对空间不同阵元接收信号的加权求和而成的。由于加权因子相当于滤波器系数,而输入的信号为空间位置不同的阵元的接收信号。所以可将数字波束形成器等同于一个空域滤波器来实现。

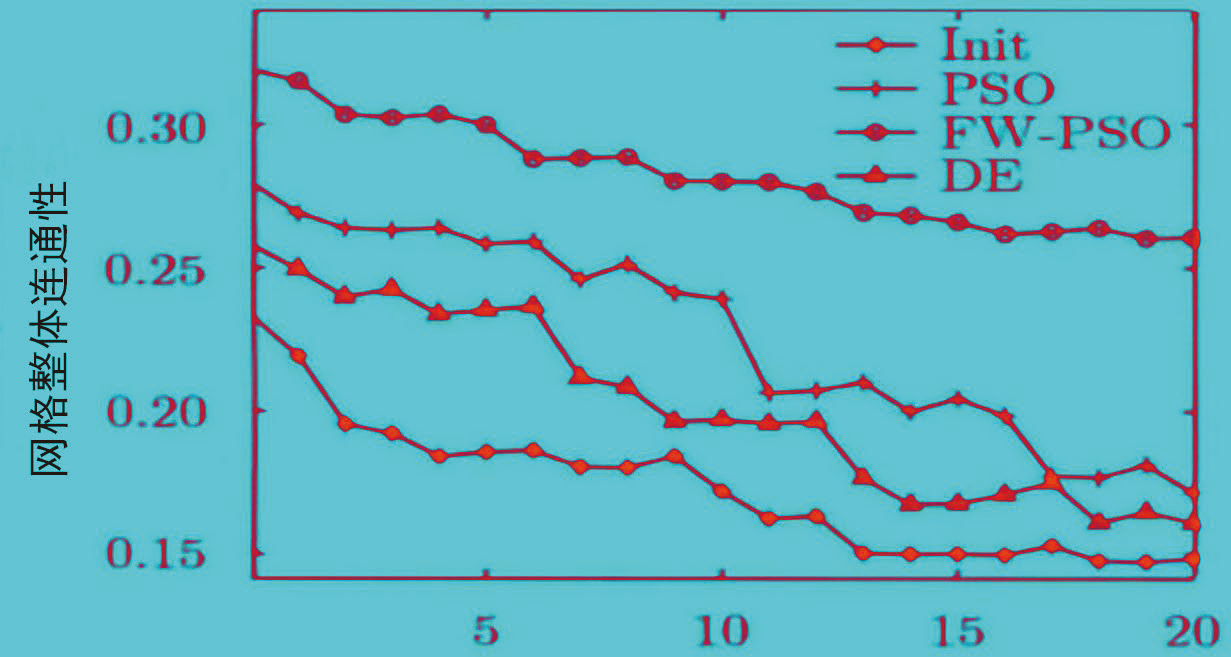

3 系统仿真与验证

本文设计核心部分是基于Stratix系列EPlS10芯片设计的分别对I/Q两路原始数据进行DLMS自适应算法和复数乘加运算,在QuartusⅡ环境下用VHDL语言编写了各功能模块,并进行了仿真,共占用了2 703个逻辑单元,同时应用Matlab对数字结果进行波形仿真,以下为仿真验证的结果。

图5为主控模块的仿真波形,其中ST0,ST1,ST2,ST3为复数乘法的4种组合,clk_regbt用来控制乘法器完成乘法,counter_bt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

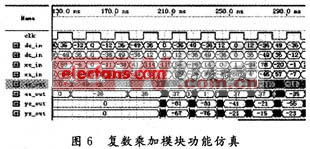

图6为复数乘加模块功能仿真结果,dc_out,ds_out,xc_out,xs_out分别是输入信号和期望信号的实部和虚部,ec_out,es_out,yc_out,ys_out分别为误差和滤波输出的实部和虚部。

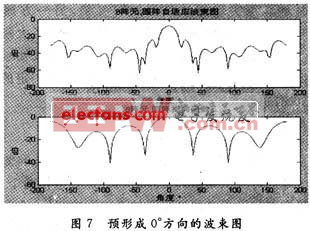

图7为系统仿真测试结果:系统预形成波束方向为0°方向,干扰从45°传来,通过仿真结果可以看出,主波束在0°方向形成,和预形成主波束吻合,在45°干扰方向形成零陷,并且提高了主波束的增益,满足系统的设计要求。

4 结 语

本文介绍了利用FPGA芯片实现的自适应BDF结构,给出了相应的硬件设计和仿真验证,采用FPGA结构,硬件成本低,在自适应阵列信号处理系统中具有很好的应用前景。

评论